基于DSP的USB数据传输系统设计

由于DSP芯片的不断发展,以及它处理数据速度快、处理数据量大的优势,已经广泛应用到数字信号处理的许多领域。在CT图像重建系统中,DSP处理的数据需要上传到PC机进行存储、显示或进行数据分析等,这就产生了PC机和DSP的数据传输问题。USB总线具有传输速度高,以及即插即用等特点,得到越来越广泛的应用,利用USB总线实现DSP和PC机的通信,从而解决图像信号的实时传输问题。Cypress公司生产的CY7C68001通用USB2.0接口控制器是基于应用层编程的接口器件,使用简单,开发方便。

在此,以TMS320C6416为例,讨论如何使用CY7C68001对TMS32OC6416进行USB接口设计,实现DSP和PC机通信,将DSP处理过的图像信号实时传到计算机中。

1 DSP与USB接口的硬件设计

TMS320C6416是TI的高性能32位定点DSP,内核采用超长指令字(VLIW)体系结构,有8个功能单元、64个32 b通用寄存器。一个时钟周期同时执行8条指令,主频可达1 GHz,处理性能高达8 000 MIPS,支持8/16/32/64 b的数据类型。

CY7C68001用来连接微处理器或DSP的DMA从装置,内部不含微处理器;支持高速(480 Mb/s)或全速(12 Mb/s)USB数据传输;提供USB 2.0协议要求的全部4种传输方式(控制传输、中断传输、批量传输和同步传输),可以满足用户对各种类型数据传输的需求。

1.1 接口的硬件设计

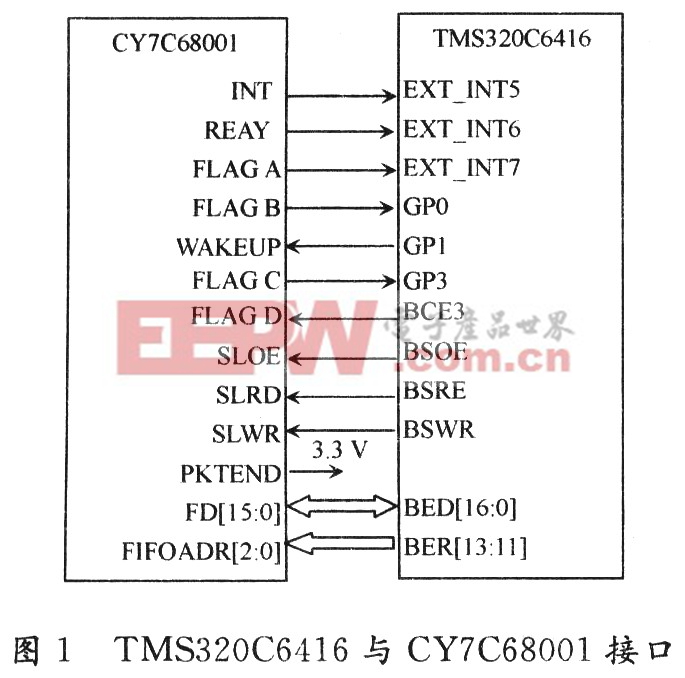

在该设计方案中,CY7C68001通过EMIFB与TMS320C6416进行异步通信,各个引脚的连接如图1所示。DSP控制CY7C68001完成DSP与PC之间的异步通信。CY7C68001的相关引脚在接口中的作用:INT:表明CY7C68001有数据将要被读出,或者有中断事件发生;READY:通知TMS320C6416可以对CY7C68001进行读写;FLAGA,FLAGB,FLAGC:反应由FAIFOADR[2:0]选择的FIFO的状态;FLAGD:为片选信号;SLOE为CY7C68001驱动数据总线;SLRD:并口读有效信号,在SLRD有效且同步通信时,FIFO指针在每个IFCLK的上升沿递增;PKTEND:总是高电平,将当前的缓冲区提交给USB;FD[15:0]:数据总线;FIFO[2:0]:提供与TMS320C6416接口的FIFO地址选择。

评论