基于FPGA的模糊PID控制器设计

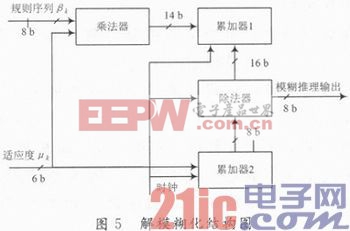

解模糊器由两个累加器、一个乘法器和一个除法器构成的。解模糊化模块接受来自于推理机的四条规则序列和它们的隶属度(在4个时钟周期内顺序接收),并产生一个明确的输出送到增益模块,如图5所示。本文引用地址://m.amcfsurvey.com/article/159601.htm

在四个连续的时钟周期内,来自推理机的隶属度和规则序列按顺序传送,而不是在一个周期内并行传输,这样可减少FPGA中的资源消耗。

2 联合仿真及结果

将设计的文件加载到FPGA器件之前,为了验证设计的正确性,必须进行全面充分的功能和时序仿真。功能仿真一般对大型设计的前期代码进行验证,通常使用Mentor公司的Modelsim来进行;时序仿真使用QuartusⅡ或Modelsim软件均可。模糊PID控制器的设计较小,省略了功能仿真步骤,直接进行时序仿真。

在设计中采用Matlab与QuartusⅡ联合仿真,不仅能够提高设计效率,而且大大增强了QuartusⅡ的仿真功能。下面介绍仿真的过程和方法。

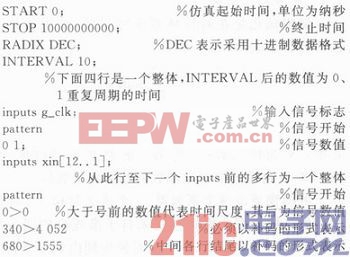

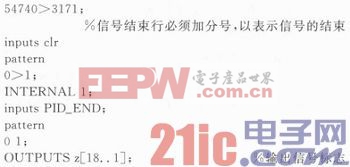

*.vec文件是QuartusⅡ与Matlab联合仿真时需要Matlab提供的文件。*.vwf和*.vec格式的文件是QuartusⅡ仿真软件中时序仿真中常用的两种文件格式。前者是在QuartusⅡ中通过波形编辑器生成的,主要用于输入简单数据,当输入较为复杂数据时,用波形输入的方法难以实现,仿真效果较差。后者是按一定仿真格式要求的文本文件输入方式,只要满足QuartusⅡ对仿真文件的格式要求,可以利用任何文本编辑器产生。为了加强数据生成处理能力,这里选用Matlab软件生成*.vec文件。*.vec文件格式及其格式说明如下:

按以上格式要求,在Matlab中将输入数据以文件的形式输出并将其保存为*.vec格式。

pid控制器相关文章:pid控制器原理

评论