基于FPGA的多通道串行A/D转换器的控制器设计

随着现代电子技术的应用和发展,越来越多的电子应用由模拟系统向数字系统转变,而A/D转换器为模拟系统和数字系统的界面,承担着模拟信号转变为数字信号的任务,在一些多路信号采集系统和实时数字信号处理系统中,A/D转换的多路扩展、高精度、低成本、实时性显得越来越重要。在一般信号采集系统中,由单片机或微控制器对高精度A/D转换器进行控制,通常采用软件模拟A/D转换器时序的方法。因此增加了CPU的负担,降低了CPU的工作效率,在多片A/D转换器多通道扩展应用中,降低了信号采集的实时性。

本文引用地址://m.amcfsurvey.com/article/163508.htm现场可编程门阵列FPGA(Field ProgrammableGate Array)是20世纪80年代中期在PAL,GAL等逻辑器件的基础上发展起来的一种可编程逻辑器件,其特点是高集成度、高速和高可靠性,设计人员可以现场修改器件的逻辑功能。VHDL(VHSIC Hardvcare Description Language)是目前通用的硬件描述语言之一,可用来描述一个数字电路的输入、输出以及相互间的行为与功能。

FPGA的高集成度和高速的特性,使之相对于单片机和微控制器,更适合用于对高速A/D器件的采样控制。本文设计一种基于FPGA的高速串行输入/输出A/D转换器的控制器,该控制器完成对ADS7844芯片的采样控制,提高了采样的实时性、减轻了主CPU的运行负担。

2 ADS7844功能介绍

ADS7844是Burr_Brown公司推出的一种高性能、宽电压、低功耗的12 b串行数模转换器。它有8个模拟输入端,可用软件编程为8通道单端输入A/D转换器或4通道差分输入A/D转换器,其转换率高达200 kHz,而线性误差和差分误差最大仅为±1 LSB。ADS7844在电源电压为2.7~5 V之间均能正常工作,最大工作电流为1 mA,进入低功耗状态后的耗电仅为3μA。ADS7844通过6线串行接口与CPU进行通信,接口简单方便。

2.1 ADS7844的引脚功能

CH0~CH7:模拟输入端,当器件被设置为单端输入时,这些引脚可分别与信号地COM构成8通道单端输入A/D转换器;当器件被设置为差分输入时,利用CH0-CH1,CH2-CH3,CH4-CH5,CH6-CH7可构成4通道差分输入A/D转换器;

COM:信号地;

Vref:参考电压输入端,最大值为电源电压;

CS:片选端、低电平有效、该脚为高电平时,其他数字接口呈三态;

Dclk:外部时钟输人端,在时钟作用下,CPU将控制字写入ADS7844,并将转换结果从中读出;

Din:串行数据输入端,在片选有效时,控制字在Dclk上升沿被逐位锁入ADS7844;

Dout:串行数据输出端,在片选有效时,转换结果在DcIk的下降沿开始被逐位从ADS7844移出;

BUSY:“忙”信号输出端,在接收到控制字的第一位数据后变低,只有在转换结束且片选有效时,该脚才输出一个高脉冲;

SHDN:电源关闭端、低电平有效。当SHDN为低电平时,ADS7844进入低功耗状态;

Vcc,GND:分别为电源端和数字地。

2.2 ADS7844的控制字及转换时序

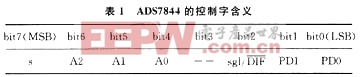

ADS7844的控制字如表1所述。

|

ADS7844的控制字共有8位,其中S是起始位,控制字的起始位总为“1”。A2~A0是通道选择位,在单端输入时分别对应8个通道,而对于差分输入,000~011分别对应CH0-CH1,CH2-CH3,CH4-CH5,CH6-CH7,而100~111则分别对应CH0-CH1,CH1-CH0,CH3-CH2,CH5-CH4,CH7-CH6。Bit3没有定义。SGL/DIF是模式控制位,该位为“1”时是单端输入模式,为“0”时是差分输入模式。PD1和PD0是电源关闭模式控制位,若为“00”,则表示ADS7844在不进行数据转换时自动进入电源关闭模式,若为“11”,芯片则始终处于电源开启模式。

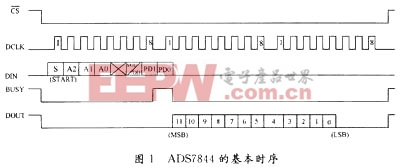

ADS7844有多种转换时序,基本时序如图1所示。

|

从图1中可见,一个转换周期需要24个时钟周期,其中8个用于输入控制字,16个用于读取转换结果。控制字的所有位在时钟上升沿被锁入芯片,转换结果在时钟的下降沿被逐位移出。所有移人和移出的数据都是高位在前、低位在后。需要说明的是,ADS7844是12位A/D转换器,其转换结果只有12位,故在移出12位结果后,还需送入4个时钟来完成整个转换过程,这4个多余的时钟移出的数据为“0”,使用时不应作为转换结果处理。

评论