基于SSI208接口模块的光电 编码器数据采集设计

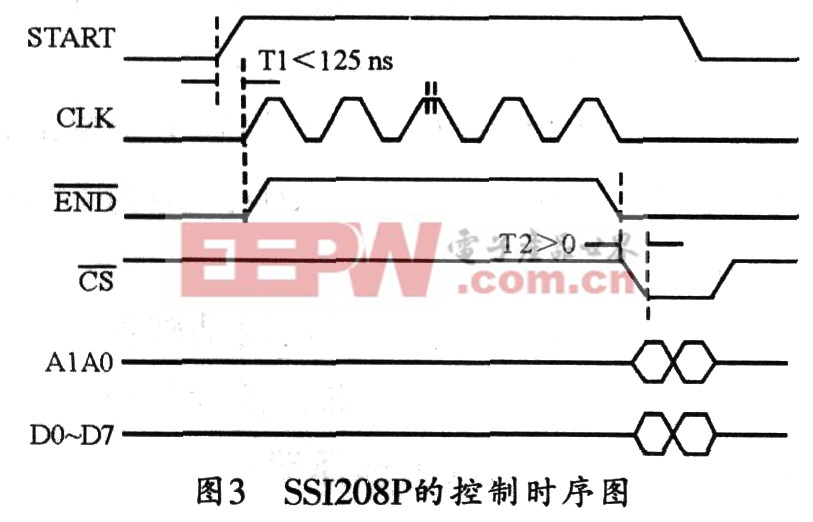

1.3SSI208P控制时序

SSI208P的控制时序如图3所示。一般可在START上升沿启动一次SSI编码器数据收发过程。START电平升高后的125ns内,SSI208P模块开始向编码器发送一帧同步时钟脉冲信号,脉冲的个数由编码器的精度决定,同时转换结束管脚END变高。发送脉冲期间,管脚END保持高电平,转换结束,END管脚电平变低后,即可从DO~D7并行读取编码器数据,每次读取八位,并由Al、AO控制输出数据的高低位,00表示读取最低八位、11表示读取最高八位。如对16位编码器,只需读取两次(A1、AO分别为00、01),最多可以读取32位数据。编码器并行数据读取结束后,应将START管脚置低,以准备启动下一次转换。本文引用地址://m.amcfsurvey.com/article/166836.htm

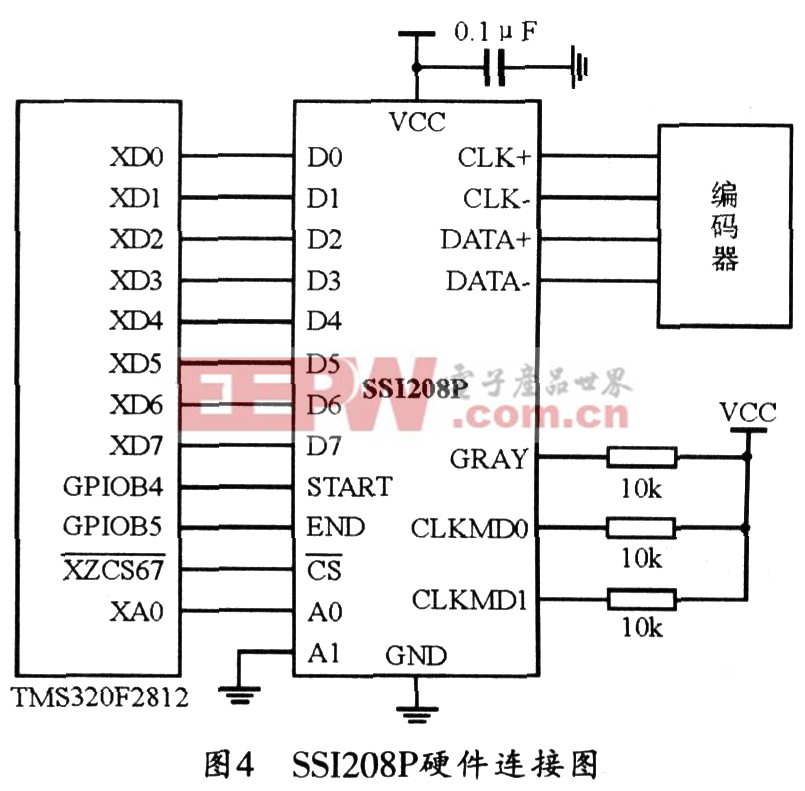

1.4基于SSI208P的接口设计

采用SSI208P模块可以大大简化单片机、DSP、PCI04等控制器扩展SSI编码器接口的软硬件设计。下面给出一种基于DSP处理器TMS320F2812的典型应用。图4所示为DSP处理器TMS320F2812与SSI208P模块的硬件连接原理图。本编码器为单圈16位绝对式角度编码器,编码器输出数据格式为格雷码,SSI208P模块的八位数据总线与TMS320F2812的低八位数据线相连。由于使用的编码器为16位,所以仅需一位地址线即可区分编码器数据的高八位和低八位,可使用外部地址片选管脚/XZCS67作为SSI208P的外部片选信号,并使用通用IO口GPIOB4控制SSI208P模块启动,同时使用通用IO口GPIOB5进行SSI208P模块转换结束状态查询。设计时应在CLKMDO、CLKMDl接上拉电阻,并将SSI208P模块同步时钟频率配置为2MHz。将GRAY管脚拉高,SSI208P模块即可将编码器输出的格雷码数据转换成BCD码。

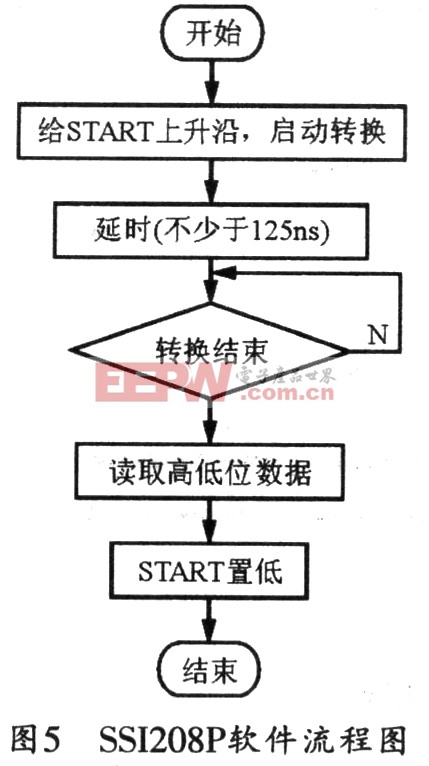

由SSI208P模块的控制时序图可以看出,SSI208P模块的启动转换控制和数据读取操作比较简单,其软件流程如图5所示。

评论