基于FPGA的图像采集系统设计与实现

1、引言

本文引用地址://m.amcfsurvey.com/article/167049.htm视频图像采集是视频信号处理系统的前端部分,正在向高速、高分辨率、高集成化、高可靠性方向发展。图像采集系统在当今工业、军事、医学各个领域都有着极其广泛的应用,如使用在远程监控、安防、远程抄表、可视电话、工业控制、图像模式识别、医疗器械等各个领域都有着广泛的应用[1]。本文介绍了一种基于FPGA的图像采集系统,用户可以根据需要对FPGA内部的逻辑模块和I/O模块重新配置,以实现系统的重构[1][2];而且采用这种设计方案 ,便于及时地发现设计中的错误,能够有效地缩短研发时间,提高工作效率。

2、系统的总体框架和工作原理

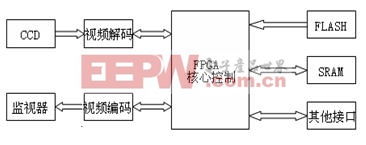

整个系统主要分为四个模块:视频解码模块、视频编码模块、存储器模块和FPGA核心控制模块,系统总体框架如图1所示。

图1 系统的总体框图

其中FPGA实现的主要功能有:视频编解码器件的初始化,视频图像的采集存储以及将采集的图像数据通过视频编码芯片送到监视器上显示。

系统的工作原理为:系统上电后,FPGA通过FLASH中的程序对完成视频解码和编码芯片的初始化配置;在接到视频AD转换的中断信号后,FPGA将转换的数字图像数据传送到SRAM保存;一帧图像转换结束后FPGA再将SRAM中的数字图像传递给视频编码芯片以便在监视器上显示,同时开始控制下一帧图像的采集。

3、硬件电路设计

3.1 AD和DA转换模块

本系统采用的视频编解码芯片是ADV7181和ADV7177,下面分别介绍AD和DA转换器件的硬件电路设计。

3.1.1 AD转换模块

ADV7181系统是AD公司推出的一款视频解码芯片[3],它具有如下特点: I2C总线接口,6通道模拟视频输入,支持NTSC、PAL、SECAM视频制式,支持多种模拟输入格式和多种数字输出格式。

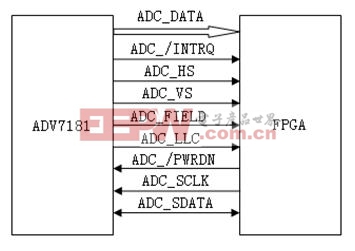

本系统中选用其中的通道1作为PAL制CVBS视频输入,数据输出可根据需要采用8位或16位的格式输出。ADV7181与FPGA的接口电路如图2所示。

图2 ADV7181与FPGA的接口电路

系统上电后通过FPGA的I2C模块完成对ADV7181的初始化配置,其中ADC_SCLK、ADC_SDATA分别为I2C总线的时钟线和数据线。ADV7181正常工作后分别输出水平同步信号ADV_HS、垂直同步信号ADV_VS、 场同步信号ADV_FIELD、中断信号ADC_/INTRQ、ADC_LLC同步信号和图像数据信号ADC_DATA(8位或16位可配置输出),另外ADC_/PWRDN信号控制ADV7181是否工作于省电模式。用户可以根据需要选择水平、垂直和场同步信号(CCIR-601格式)或ADC¬_LLC信号(CCIR-656格式)来实现系统与视频输入的同步,并利用这些同步信号控制对转换完成的视频数据的写存储器操作。

3.1.2 DA转换模块

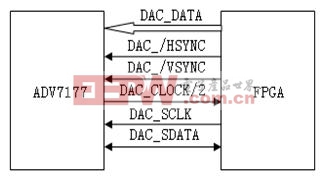

DA转换采用的是AD公司的ADV7177[4],它具有如下特点:I2C接口,3路模拟视频输出,支持多种数字输入格式和多种模拟输出格式,用户可根据需要选择使用。它的电路设计与ADV7181类似,ADV7177与FPGA的接口电路如图3所示。

图3 ADV7177与FPGA的接口电路

其中DAC_DATA为输入数字视频信号,DAC_/HSYNC、DAC_/VSYNC分别为水平和垂直同步信号,DAC_CLOCK2为ADV7177输出的27M或13.5M同步时钟( 与寄存器的配置数据有关),DAC_SCLK、DAC_SDATA为ADV7177的I2C配置总线。

3.2 FPGA核心控制模块

FPGA核心控制模块采用的是ALTERA公司Cyclone II系列的EP2C20[5],它具有较高的性价比:EP2C20最多用户管脚数为315,四个PLL,26个嵌入式18*18乘法器,52个M4K RAM块,186752个逻辑单元;共分8个I/O Bank,每个Bank可以根据需要配置为1.2V或3.3V的I/O电平,方便与外围电路连接。考虑到系统的实际需求,在该系统中采用具有240个引脚PQFP封装的EP2C20Q240。

在该系统中,FPGA主要完成对视频AD、DA的初始化配置和存储器的读写控制,它通过AD的中断信号完成对视频数据的采集,并将采集的数据放到存储模块中,当采集完一帧后将数据传递给视频编码芯片并在监视器上显示同时开始采集下一帧图像。

在本系统中FPGA采用了JTAG和AS两种配置模式,具体的设计可参考ALTERA数据手册[5]。

3.3 存储器及其他模块

由于FPGA芯片内部的RAM资源有限,不能存储过多的视频数据并对其进行处理,因此在本系统设计中,外加了两片SRAM芯片来辅助FPGA进行视频信号采集。两片SRAM可以进行16位的数据存储,这样ADV7181和ADV7177可以根据需要配置为8位或16位数据的工作模式,提高了系统的灵活性。

本系统设计中采用的SRAM芯片是美国IDT公司生产的IDT71V424[6],它是采用高性能与可靠性的CMOS工艺生产的高速静态存储器,其单片存储容量为512K*8Bit,具有高速的访问时间,10或12ns。其内部完全由静态异步电路构成,无需输入时钟信号,也不必对芯片进行刷新,即可直接对无用数据进行覆盖。

在实际的设计中为了保证控制信号的有效性,3条控制线SRAM_/WE、SRAM_/OE, SRAM_/CS分别加了一个4.7K的上拉电阻后才与FPGA芯片连接。具体电路如图4所示:

图4 SRAM与FPGA的接口电路

此外,为了减少模拟与数字系统之间的相互干扰,电源模块采用的是数字电源和模拟电源分开设计最后一点共地的设计方案。主要采用了TI公司的TPS54612、TPS64616分别提供FPGA 1.2V核心电压和3.3V IO电压;模拟1.8V和3.3V采用的是AMS1117系列的电源芯片。

4、系统软件设计

本系统软件是在Quartus II 环境下采用Verilog语言开发完成的。主要包括:1、AD和DA芯片的初始化配置,2、视频图像的采集,3、视频图像的存储与DA转换。

评论