电能计量芯片Sigma-Delta ADC降采样滤波器设计(一)

0 引 言

本文引用地址://m.amcfsurvey.com/article/174623.htm智能电表(smart meter)作为智能电网的终端计量仪器,不仅需要能够精确计量用户的用电信息,而且还需各种通信功能,如RS485.红外.电力线载波等,以实现自动化远程管理.因此,智能电表在整个智能电网的建设中起着关键性作用.而对于智能电表的核心---电能计量专用芯片(Electrical Measurement Unit,EMU)也提出了更高的要求.目前计量芯片的模数转换电路基本上都采用Sigma-Delta 型,而降采样滤波器是Sigma-Delta ADC 的核心组成部分,因此,对降采样滤波器的研究具有十分重要的意义.

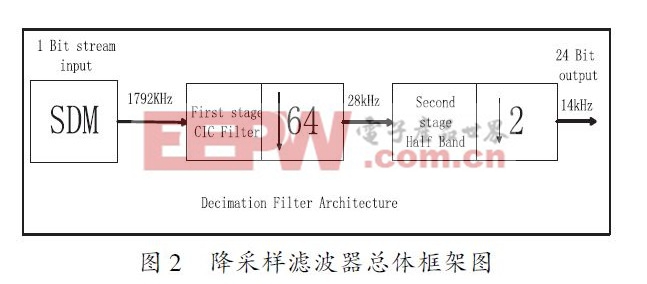

在Sigma-Delta ADC 中,功耗主要集中在降采样滤波器 .而滤波器的功耗主要由乘法器决定,因此如何减少滤波器中乘法器的个数成为降采样设计的研究重点.HOGENAUE 提出了级联积分梳状滤波器(Cascaded Integrator Com,CIC),由于CIC滤波器无须乘法运算,因此与传统通过FIR 滤波器直接降采样相比,极大地降低了面积与功耗.然而当降采样率较大时,单级CIC 滤波器却无法满足要求,且功耗也相对较大.多级采样交换理论及多相原理从而降低乘法运算次数,该方法的难点在于多相因子的不确定性,且不同的多相因子得到的滤波器结构不一样,功耗也不一样.串行算法实现CIC 从而降低功耗,但串行方法不适合计量芯片中并行的数据处理.文中提出了一种级联抽取的方法,不仅结构简单,也易于实现,完全满足电能计量的需求.前级为CIC 滤波器,后级为HBF 滤波器,实现128 倍的抽取.由于HBF 只适用于2 倍抽取,因此前级CIC 降采样率为64 倍.对HBF 的非零系数采用有符号CSD 编码,进一步减少了电路功耗.

1 CIC 滤波器原理及设计

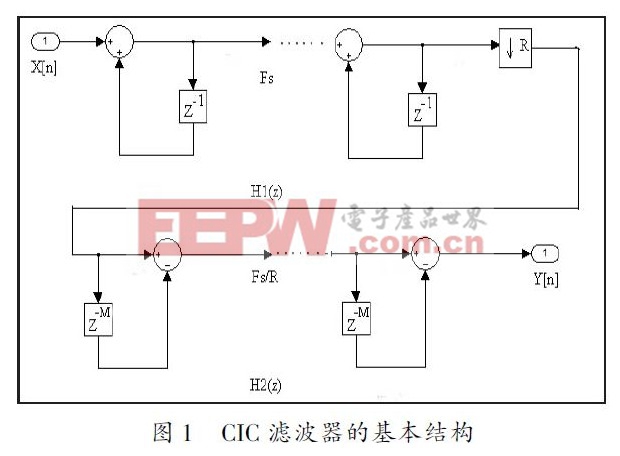

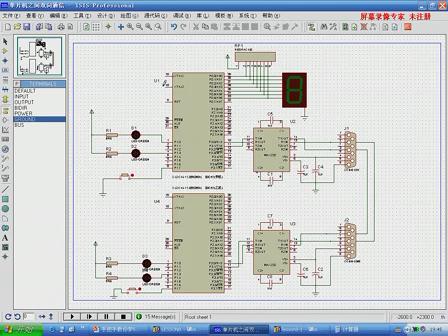

CIC 滤波器的基本结构如图1 所示,由积分级和梳状级级联组成.

积分级采样频率为FS ,它的传递函数:

降采样的倍数为R,相对于积分级,梳状级的采样频率为FS / R,它的传递函数:

其中M 为延迟因子,控制梳状级的频率响应,在设计中,M 的取值一般为1 或2.

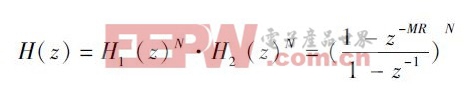

假设CIC 滤波器有N 阶,那么总的传递函数为 :

幅值响应为:

CIC 滤波器的优点是结构非常有规律,由若干级积分级与梳状级级联组成,且内部无须乘法运算,因此,在变速率系统中得到了广泛的应用.但随着降采样率的增加,内部寄存器的宽度以及功耗将会成倍的增加.电能计量芯片Sigma – Delta 的采样频率为1792kHz,后续数字信号处理的频率为14kHz,因此,在本设计中,为了实现128 倍的降采样,采用了分级抽取的方法.降采样滤波器的总体框架如图2 所示 .

评论