基于集成计数器的N进制计数器设计与仿真

摘要:计数器是一种重要的时序逻辑电路,广泛应用于各类数字系统中。介绍以集成计数器74LS161和74LS160为基础,用归零法设计N进制计数器的原理与步骤。用此方法设计了3种36进制计数器,并用Multisim10软件进行仿真。计算机仿真结果表明设计的计数器实现了36进制计数的功能。基于集成计数器的N进制计数器设计方法简单、可行,运用Multisim10进行电子电路设计和仿真具有省时、低成本、高效率的优越性。

关键词:电路设计;仿真;计数器;归零法;Multisim10

计数器是记忆时钟脉冲个数的数字电路,作为一种最典型的时序逻辑电路,在各类数字系统中有着广泛的应用。计数器的设计方法主要有两种,1)以时钟触发器为核心加上必要的门电路进行设计;2)利用集成计数器构建,这种方法从设计原理到硬件实现都相对简单,因而较为常用。基于集成计数器的N进制计数器设计方法有归零法和置数法。文中以最常用的4位二进制(十六进制)同步加法计数器74LS161及十进制同步加法计数器74LS160为核心,以三十六进制为例,介绍了归零法设计N进制计数器的方法,并用Multisim10软件进行仿真。Multisim10软件由美国国家仪器(National Instruments,NI)公司于2007年推出,该软件具有以下特点:1)直观的图形界面;2)庞大的元器件库;3)丰富的测试仪器;4)完备的分析工具;5)强大的仿真能力;广泛应用于电子电路的教学、设计和科研中。

1 归零法设计原理

1.1 集成计数器功能描述

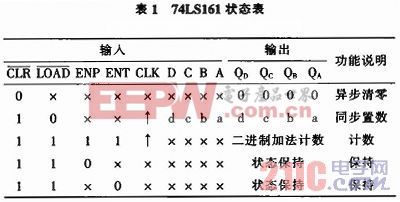

集成计数器由芯片厂家生产后,其功能已固化在集成芯片中,其功能常用状态表描述。表1是4位二进制同步加法计数器74LS161的状态表,表中![]() 是异步清零控制端,低电平有效;

是异步清零控制端,低电平有效;![]() 是同步置数控制端,低电平有效;ENP和ENT是计数器工作状态控制端,高电平计数;CLK是计数脉冲输入端;D、C、B、A是并行数据输入端;QD、QC、QB、QA是计数器状态输出端;“×”表示任意状态,“↑”表示时钟脉冲上升沿。

是同步置数控制端,低电平有效;ENP和ENT是计数器工作状态控制端,高电平计数;CLK是计数脉冲输入端;D、C、B、A是并行数据输入端;QD、QC、QB、QA是计数器状态输出端;“×”表示任意状态,“↑”表示时钟脉冲上升沿。

十进制同步加法计数器74LS160的状态表与74LS161类似,区别在于计数状态是按十进制(8421BCD码表示)规律变化。

1.2 归零法设计原理

设现有M进制集成计数器,设计N进制计数器。若M>N,从全零初始状态S0开始计数,第1个时钟到来时,计数状态为S1,第N-1时钟到来时,计数状态为SN-1,第N时钟到来时,利用集成计数器的清零端或是置数端,使计数状态返回全零初始状态S0,原M进制集成计数器中的SN~SM-1这M-N个状态被跳过。若集成计数器的清零端为异步控制方式,具体设计与仿真步骤为:

1)确定最大计数状态SN(过渡状态),并写出SN的二进制代码:

2)根据状态SN的非完全译码,求归零逻辑,即清零端控制信号的逻辑表达式;

3)在仿真平台Multisim中选择器件,根据归零逻辑创建仿真电路;

4)选择时钟信号源输入,示波器或数码管等作为测量或显示仪器,运行仿真电路,观测结果。

评论