RocketIOTM GTP在串行高速接口中的位宽设计

无论是在传输还是在操作过程中,都要保证每个Dword的正确性和完整性,否则将导致数据出错或原语流失。

另外,目前高速数据传输接口或总线常用8B/10B编码来编码,其根本目的是实现直流平衡(DC Balance)。当高速串行流的逻辑1或逻辑0有多个位没有变化时,信号的转换就会因为电压位阶的关系而造成信号错误。直流平衡的最大好处便是可以克服以上问题。8B/10B编码是目前许多高速串行总线采用的一种编码机制,如1394b、Serial ATA、PCI Express、Infini-band、Fiber Channel、RapidIO等总线或网络,都是8B/10B编码的拥护者。该编码技术的基本精神很简单,就是将8个位经过映射的机制转化为10个位的字码,但它平衡了位流中0与l的数量。

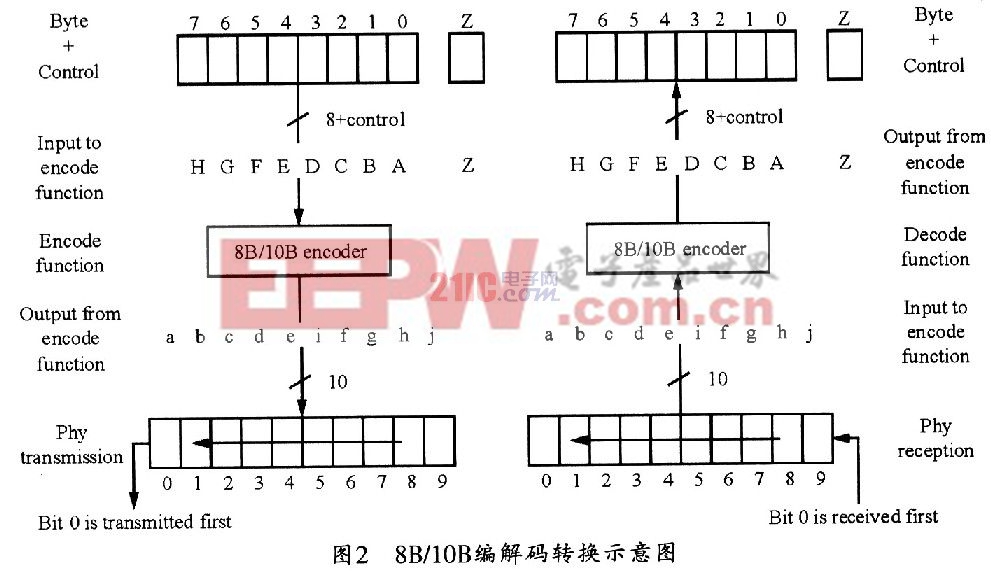

8B/10B编码是将一组连续的8位数据分解成两组数据,一组3位,一组5位,经过编码后分别构成一组4位代码和一组6位代码,从而组成一组10位的数据发送出去。相反,解码是将l组10位的输入数据经过变换得到8位数据位。其8B/10B编解码过程如图2所示。本文引用地址://m.amcfsurvey.com/article/180728.htm

Xilinx公司推出的Virtex-5 FPGA以及配套的Virtex-5 RocketI0TMGTP收发器只支持16bit接口位宽的数据传输,即该GTP收发器是以word为数据处理单位。由于这与SATA2.0协议的相关规定出现了偏差,因而要求在数据进入设计主体逻辑前后要进行合并以及分解。同时,FPGA中设计的数据处理逻辑是根据协议的要求而定义为75 MHz的时钟域来进行处理的,因此,在将数据交给FPGA中的数据处理主体逻辑之前,也必须进行位宽的转换。

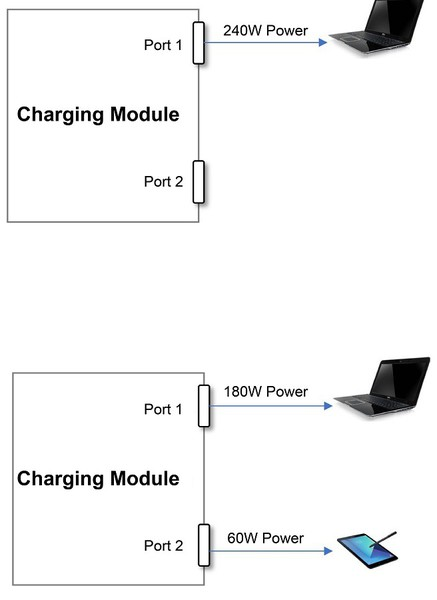

由于GTP附带的2 bit控制字节指示信号rxcharisk可用以表征接收到了K字符,故实际的数据需要从150 MHz (16+2) bit转换为75 MHz(32+4)bit。但由于16 bit和32 bit的并行数据是主体。因此,笔者仍称之为16 bit到32 bit位宽转换和32bit到16 bit位宽转换,它们实际上都包含了指示信号,用来标示该字符是否是控制字符。

2 位宽转换

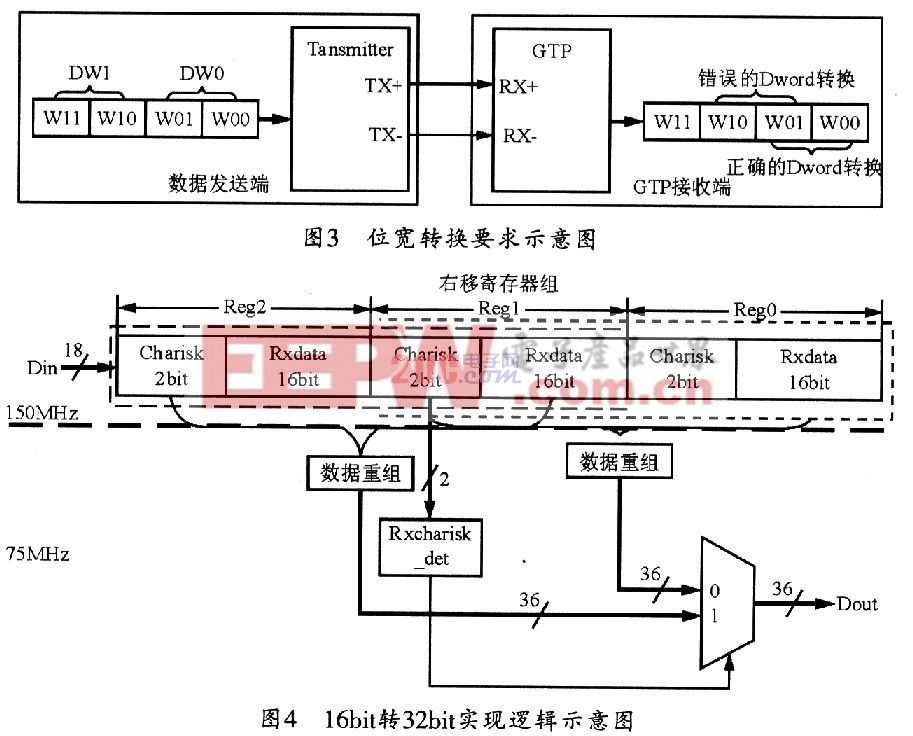

根据SATA2.0协议的规定和Virrex-5RocketIOTMGTP的特性,以及SATA2.0接口逻辑中需要提取原语(primitive)进行逻辑控制的要求,16bit和32 bit位宽的相互转换不能简单的进行word合并拆解,而是需要实现图1中wordO和wordl的正确组合,否则将导致原语或数据受损,使控制逻辑无法获得有效的交互原语,数据处理逻辑组帧传输错误,文件损坏的状况发生。这就要求系统能够在提取原语和数据组帧之前,及时进行Dword边界校正,以保证后续处理的正确。

2.1 16bit至32bit位宽转换模块

该模块将GTP接收后的150 MHz 16 bit并行数据转换成数据处理逻辑可以工作的75 MHz 32 bit的并行数据。图3所示为其位宽转换要求示意图。

由于在转换开始时,必须正确地将2个相关的16 bit Word组合成一个32bit DW,但不能将一个DW的低字跟相邻的一个DW的高字组合成一个DW,否则逻辑处理时就会出错。图4所示是16Bit转32 bit的实现逻辑示意图。

评论