一款高性能共源共栅运算放大器设计

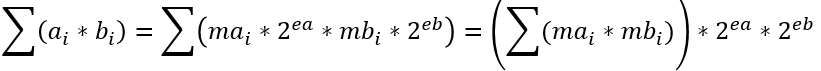

式中:fp1为运放主极点;fp2运放非主极点;fz为运放零点。在复用型折叠式共源共栅运放中,主极点是由时间常数RORFC CL决定,非主极点由M5,M6源端寄生电容C2和该点的电阻R2的乘积决定。为了使运放的相位裕度保持在60°以上,必须使得非主极点频率大于2.2倍增益带宽。在复用型折叠式共源共栅中,M5,M4源端的寄生电容为:

C2=CGS5+CSB5+CGD3a+CdB3a+CGD1a+CdB1a

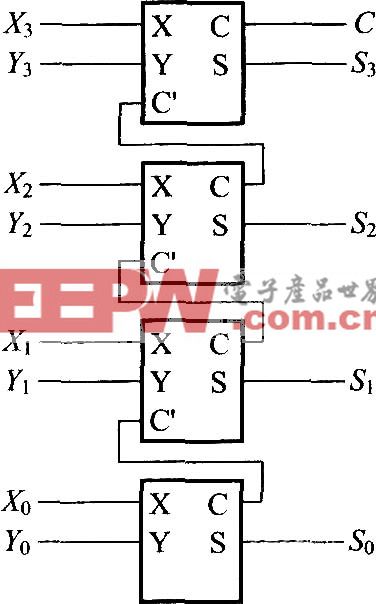

在图3中,M1a的电流I1a与M5的电流I5都流过M3a,M3a必须要有足够的栅宽以满足在比较小的驱动电压下能传导大电流,所以寄生电容CGD3a和CdB3a相当大。f2=1/(C2R2),C2大,f2就会变小。要使f2大于2.2倍增益带宽,必须推高f2。用减少流入M3a和M4a的电流的方法就可以达到目的。因为电流减小,M3a和M4a的栅宽也相应减小,从而C2也减小,f2便增大。

2 电路仿真结果

图2中各个MOS管的参数如表1所示。

所设计的电路仿真用Cadence公司的模拟仿真工具Spectre,仿真模型用CSMC0.5 μm标准CMOS工艺模型。电路交流仿真结果见图3。由图中增益曲线看出曲线在频率10 kHz处开始下降,所以带宽为10 kHz,增益为71.7 dB。频率大于10 kHz,其增益开始降低,降低到0 dB处的频率为增益带宽,值为52.79 MHz。由图中相位曲线看出,增益降为0 dB时,相位为-119.55°,相位裕度就为60.45°。所以电路增益带宽为52.79 MHz,低频增益为71.7 dB,相位裕度为60.45°。与文献中折叠式共源共栅运算放大器的增益带宽4.05 MHz,低频开环增益43.5 dB,相位裕度59°相比,其在增益,带宽和系统稳定性上都有很大提高。

3 结语

本文在文献中折叠共源共栅运放和复用型折叠共源共栅运放的分析基础上,设计了一种高性能折叠共源共栅单级运放,具有高开环低频增益、高增益带宽。采用CSMC0.5μm标准CMOS工艺模型,Cadence公司的模拟仿真工具Spectre对电路进行直流和交流仿真。结果表明:电路的增益带宽为52.79 MHz,低频开环增益为71.7 dB,相位裕度为60.45°,其各项指标与均有较大提高,设计令人满意。

漏电开关相关文章:漏电开关原理

评论