基于FPGA的视频采集显示系统

摘要设计实现一种基于FPGA的视频采集显示系统,包括视频图像的采集、处理与显示3个部分。视频图像部分采用CCD摄像头OV7670作为视频数据的采集,利用在FPGA中构建FIFO并配合SDRAM高速读写实现视频图像数据的高速缓存处理,使用FPGA中构建的Nios Il嵌入式内核,实现对SDRAM的控制以及视频数据的TFT液晶实时显示。整个系统获得了较好图像采集、显示效果。

关键词FPGA;视频处理;TFT LCD;Nios II

随着高品质实时视频显示技术低,民用领域如天气预报、资源探测、机器人视觉以及各种医学图像的实时分析;军用领域如导弹精确制导、战场动态分析等,均需要高质量实时视频显示系统的支持。近年来低成本的FPGA(Filed Programmable Gate Array)不断推陈出新,利用EDA工具对FPGA芯片进行多样性设计,已经成为电子设计的通用平台,并逐步向支持系统级设计的方向发展。与专用集成电路相比,FPGA芯片

具有快速的定制性和高灵活性,扩展性强的特点。作为一个平台,FPGA已适用于高性能低成本的视频和图像处理,尤其在图像分辨率和帧率要求较高的场合。

设计采用CMOS图像传感器OV7670对外界图像进行实时采集,通过FPGA内部设计的初始化模块对图像传感器输出信号的格式进行配置。根据其输出信号的时序,在FPGA内部设计采集单元。采集到的数据经过格式转换送到内部配置的Nios II嵌入式内核,Nios II嵌入式内核将实现LCD显示屏控制与视频数据的实时显示。

1 系统总体设计

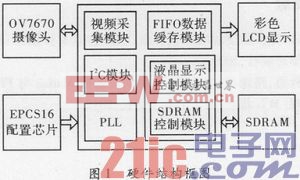

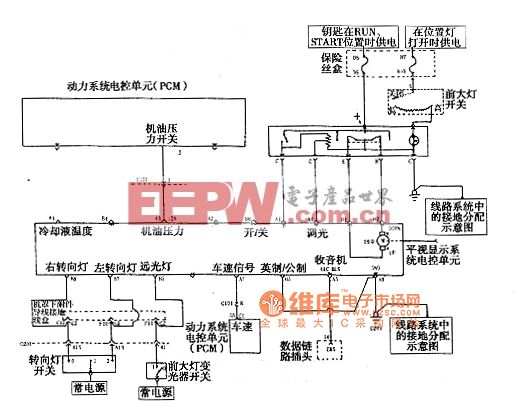

基于FPGA实现的视频显示系统的整体结构框图如图1所示。系统主要分为:视频采集模块、PLL锁相环时钟管理模块、I2C总线模块、FI FO视频数据处理模块、Nios II显示控制模块。系统中PLL负责为NiosII嵌入式内核、外部SDRAM和OV7670摄像头提供时钟,系统通电后,FPGA首先从EPCS中读取配置数据,完成自身程序加载,随后对系统时钟分频为摄像头提供系统时钟,然后通过I2C总线完成对OV7670摄像头的配置。

配置完成后,OV7670将采集到的视频数据输出格式转换成RGB565标准的视频数据及图像时钟送入FPGA进行处理,并将处理后的图像数据通过FIFO模块暂时存储在SDRAM中进行缓冲,同时Nios II模块读取存放在SDRAM中的视频图像数据,按照TFT液晶显示的时序、数据要求将视频图像数据送到TFT彩色液晶显示屏上显示。

1.1 FPGA选型

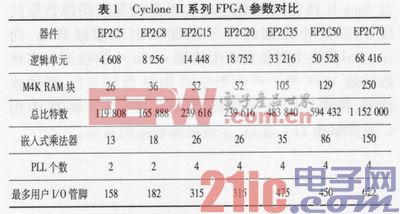

FPGA是该系统的核心,由于系统目前只是完成简单的图像处理,故FPGA选用Altera公司的低成本FPGA Cyclone II系列器件。Cyclone II系列器件简介如表1所示。

Cyclone II器件采用90 nm工艺制造,它延续Cyclone的低成本定位,在逻辑容量、PLL、乘法器和I/O数量上都比Cyclone有了较大提高,应用Cyclone II进行图像处理开发有如下优点:(1)低成本高性能,适应图像处理要求较高的需要。(2)丰富的内嵌存储器资源,适应大量图像数据存取的需要。(3)丰富的硬件乘法器,适应图像处理算法的需要。系统的FPGA选用开发板自带的EP2C5Q208C8芯片。

fpga相关文章:fpga是什么

摄像头相关文章:摄像头原理

锁相环相关文章:锁相环原理

评论