加速FPGA系统实时调试技术

摘要:随着FPGA的设计速度、尺寸和复杂度明显增长,在整个设计流程中的实时验证和调试部分成为当前FPGA系统的关键部分。获得FPGA内部信号有限、FPGA封装和印刷电路板(PCB)电气噪声,这一切使得设计调试和检验变成设计周期中最困难的流程。本文重点介绍在调试FPGA系统时遇到的问题及有助于提高调试效率的技术,通过逻辑分析仪配合FPGA View软件快速有效的观测FPGA内部节点信号。最后提供了FPGA具体的调试过程和方法。

本文引用地址://m.amcfsurvey.com/article/189811.htm引言

随着FPGA的设计速度、尺寸和复杂度明显增长,使得整个设计流程中的实时验证和调试成为当前FPGA系统的关键部分。获得FPGA内部信号有限、FPGA封装和印刷电路板(PCB)电气噪声,这一切使得设计调试和检验变成设计周期中最困难的流程。另一方面,几乎当前所有的像CPU、DSP、ASIC等高速芯片的总线,除了提供高速并行总线接口外,正迅速向高速串行接口的方向发展,FPGA也不例外,每一条物理链路的速度从600Mbps到高达10Gbps,高速I/O的测试和验证更成为传统专注于FPGA内部逻辑设计的设计人员面临的巨大挑战。这些挑战使设计人员非常容

易会把绝大部分设计周期时间放在调试和检验设计上。

为帮助您完成设计调试和检验流程,它需要使用新的调试和测试工具,帮助调试设计,同时支持在FPGA上全速运行。

本文重点介绍在调试FPGA系统时遇到的问题及有助于提高调试效率的技术,针对Altera和Xilinx的FPGA调试提供了最新的方法和工具。

FPGA设计流程概述

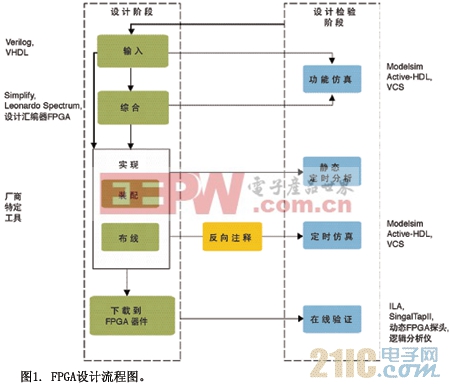

在FPGA系统设计完成前,有两个不同的阶段:设计阶段,调试和检验阶段(参见图1)。设计阶段的主要任务是输入、仿真和实现。调试和检验阶段的主要任务是检验设计,校正发现的任何错误。

[图示内容:]

Simplify, Leonardo Spectrum, Design Compiler FPGA: Simplify, Leonardo Spectrum, 设计汇编器FPGA

Vendor Specific Tools: 厂商特定工具

Design Phase: 设计阶段

Entry: 输入

Synthesis: 综合

Implementation: 实现

Place: 装配

Route: 布线

Download to FPGA Device: 下载到FPGA器件

Back Annotation: 反向注释

Debug Verification Phase: 设计检验阶段:

Functional Simulation: 功能仿真

Static Timing Analysis: 静态定时分析

Timing Simulation: 定时仿真

In-Circuit Verification: 在线验证

ILA, SingalTap, Dynamic FPGA Probe, Logic Analyzer: ILA, SingalTapII, 动态FPGA探头, 逻辑分析仪

评论