基于Camera接口的船用导航雷达显示设计

摘要介绍了基于ARM的Camera接口船用导航雷达显示设计。通过FPGA将雷达回波转换成ITU—R BT601/656视频信号,将视频信号送入ARM的Camera接口,存贮在帧缓存存储器,ARM的显示控制器以DMA的方式读取帧缓存数据,与人机界面在显示控制内部混合叠加后直接送显示器显示。该设计实现了雷达的回波和人机界面的同步显示,满足了船用导航雷达系统的显示要求,并在工程上验证了该设计的有效性。

关键词雷达;FPGA;Camera;显示控制器;同步显示

船用导航雷达是测定本船位置和预防冲撞事故不可缺少的系统,其能够准确捕获其他船只、陆地、航线标志等物标信息,并将其显示在显示屏上。船用导航雷达与军用雷达相比成本较低,因此多采用基于嵌入式ARM(Advanced RISC Machines)设计的小型化平台。小型化平台计算机软件实现回波显示的方式,对计算机资源的开销较大,且实时的回波显示对软件的处理流程要求也较高,因此实现回波显示硬件设计成为必要。

通过FPGA(Field Programmable Gate Array)将雷达回波转化成视频信号,送至ARM的Camera接口,以视频图像的方式与人机界面在显示控制内部混合叠加,实现雷达的回波和人机界面的同步显示,成为解决小型化雷达终端回波显示的可行方案。

1 工作原理

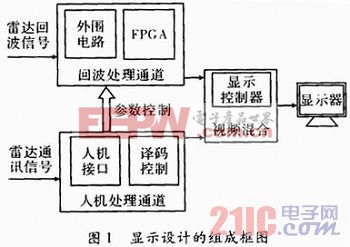

船用导航终端显示设计的组成框图如图1所示,主要由3部分组成。回波处理通道由FPGA和外围电路组成,主要完成雷达信号接口匹配、回波采样、回波峰选处理、扫描坐标变换处理、余辉尾迹控制、时序控制和视频格式编码等功能。人机处理通道由ARM计算机组成,由载入的软件完成二次显示信息处理、操控窗口控制、工作参数设置以及与系统和整机的通信等。视频混合模块由ARM的显示控制器实现,在行、场同步控制信号的控制下,DMA(Direct Memory Access)的方式读取系统内存中显示数据,完成雷达回波和人机接口的叠加显示。

2显示设计及实现

船用导航雷达终端的显示设计主要有回波的实时校正、回波近区覆盖/远区分裂补偿、ITU—R BT601/656视频编码、显示控制器混合叠加等多个功能模块的设计。

2.1 雷达回波数据的峰选实时校正

显示器半径的像素数量一般不等于雷达触发的距离采样数量,所以回波的显示处理均需要峰选。峰选就是将显示量程内的所有回波采样值按显示像素分组,在每组内选择最大值作为对应显示像素的辉度值,每组回波采样值的数目为峰选系数,按照峰选系数进行处理。峰选系数N由式(1)计算,N一般取小数点后两位![]()

式中,N为峰选系数;R为显示量程,单位km;f为峰选始终频率,单位MHz;M为显示像素。

软件根据显示模式及量程计算出峰选系数后,由端口置入FPGA,FPGA根据峰选系数,将对应的峰选校正值存贮在内部ROM(Read-Only Memory)中,实时读取校正。

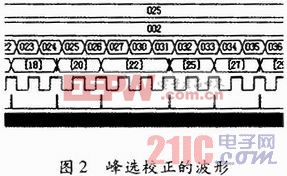

例如,峰选系数为2.25,在Altera Quartus中仿真的波形如图2所示。

评论