基于Nios II处理器的SVPWM IP Core设计

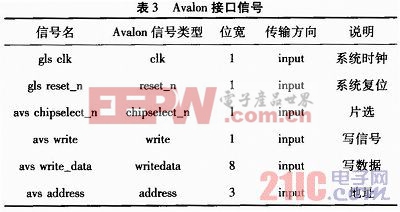

(2)Avalon接口设计。

Avalon接口为SVPWMIPCore提供了一个标准的Avalon从端口,通过此接口按照Avalon从端口的传输协议对IPCore进行控制,相关的Avalon接口信息如表3所示。本文引用地址://m.amcfsurvey.com/article/190673.htm

(3)乘法因子计算模块。

这里的乘法因子是指式(6)和式(7)中的方括号内运算的结果。本模块根据外部A/D转换的结果、设定的TPWM及预期的参考电压矢量的数值,计算出式(6),式(7)的方括号内的结果,用于乘法模块中对ta和tb的计算。

(4)数据存储模块。

sinθ及sin(π/3-θ)在扩大255倍后,分别作为高8位和低8位存储在容量为128×16 bit的ROM中,从而可以同时读取分别用于式(6)中tb和式(7)中ta的计算。时序控制ROM的容量为32×3 bit,存储表1中的开关时序,其高3位地址用于对6个扇区编码,最低2位地址用于某区间内的时序控制,由于在同一区间中采用升降计数,根据表1中桥臂开关切换的对称性可知,只要两位地址即可存储时序控制信号。

(5)数据选择器。

当0≤θπ/6时,利用正弦值存储模块输出数据的高8位计算tb,利用低8位计算ta;而当θ值为π/6≤θπ/3时,则应该利用低8位计算tb,利用高8位计算ta。通过数据选择器实现高、低8位的交换。

(6)时序控制模块及IGBT时序控制ROM。

时序控制模块根据当前所处的扇区、ta、tb及当前PWM的计数值生成IGBT时序控制ROM的地址。IGBT时序控制ROM中存储的是桥臂开关控制的时序,根据时序控制模块输出的地址,将存储在ROM中的开关控制量读出后送至死区发生器模块。

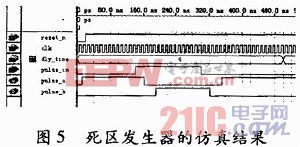

(7)死区发生器模块。

死区发生器模块用于将桥臂上部IGBT管的3个时序控制信号,变为用户设定死区时间的3组信号,对6个IGBT管进行控制,死区时间在0~6.3μs之间设置,步进值0.1μs。死区发生器仿真结果如图5所示,输入信号为pulse_in,输出信号为pulse_a和pulse_b,死区时间设置为0.4μs。

3 设计验证

各模块设计完成后,用原理图方式完成系统设计如图4所示,在SOPC Builder中将之作为自定义组件添加到系统中生成IPCore。设计验证在Altera公司的DE2开发板上进行,将该IP Core添加到SOPC工程中,编译、下载到FPGA芯片中,运行测试程序后,利用SignalTapII Logic AnMyer捕捉到桥臂上方3个IGBT管的控制信号如图6所示。图中的sector是为方便测试而引出的扇区编号信号,由图可知设计正确。

4 结束语

设计了一个结构简单、性能良好的SVPWMIP核,并在NiosII平台下将其封装成一个模块化的独立元件,使之易于在其他的工程中复用,利用该IP核可以方便地构建基于NiosII嵌入式处理器的SVPWM控制系统,体现了SOPC嵌入式系统的灵活性和扩展性。

评论