PCI总线从设备接口的CPLD实现

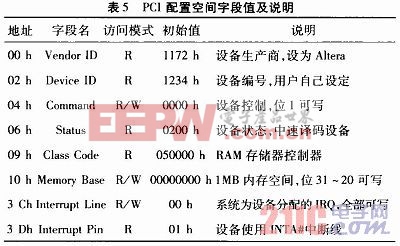

2.2 配置空间

配置空间是容量为256 Byte并具有特定记录结构或模型的地址空间,包括头标区和设备有关区,前64 Byte是头标区,用来唯一的识别设备,并使设备能以一般的方法控制,是PCI设备必须实现的。

本模块实现了头标区所有的字段,可读可写字段中可写的位由触发器来实现,其它位和只读字段全部硬件连线接地或者接高。通过配置空间寄存器,配置软件可以确定设备的存在、功能以及资源请求。配置空间主要字段的设置及含义说明如表5所示。本文引用地址://m.amcfsurvey.com/article/190766.htm

2.3 译码

译码模块包括命令译码、地址译码。在总线交易的地址期,译码模块通过将AD信号线地址期的值与配置空间基址寄存器值相比较,确定访问是否落在本设备的地址空间范围内;或确定是否被选作配置访问的目标设备。同时对地址期C/BE信号线的值进行命令译码,确定总线访问的类型,本模块支持配置读、写和内存读、写4种PCI总线访问方式。若译码后设备被选中,则发送HIT信号通知状态机做进一步处理。

2.4 数据通道

在总线交易的地址期,数据通道锁存AD总线上的地址信号,并在IRDY#和TRDY#同时有效的时钟上升沿,将地址自动增加一个双字地址并提供给用户接口。

在数据期,写交易时将AD总线上的数据写入配置空间或者用户设备,在读交易时数据通道负责将要读出的配置数据或用户设备数据锁存送到AD总线上,并产生偶校验值送给奇偶校验模块。数据通道为PCI访问配置空间和用户设备提供了一个地址和数据接口。

2.5 奇偶校验

奇偶校验主要用来确定主设备是否成功的寻址到它希望的目标设备,以及数据传输的正确与否,在总线交易中,任何设备驱动数据总线输出数据,就必须在相应的地址或者数据的下一个时钟周期驱动PAR线。设计中省去了奇偶校验值的检验电路,只实现了必须的偶校验值产生电路,计算出要输出数据和CBE的偶校验值后,在数据期的下一个总线时钟周期送给主设备检验。

2.6 重试模块

从设备接口如果承诺了一个数据交易,则必须在16个时钟周期内准备好发送和接受数据,否则超时重试。如果用户设备被选作交易的从设备,但没有准备好,无法开始起始字节的数据交易,则状态机一直处于等待状态,如果在规定的时间内用户设备仍没有有效Ready信号,该模块通知状态机超时重试,然后断开连接。

2.7 其他逻辑

该部分主要包括一个总线选择器和一个三态总线驱动器。总线选择器根据总线访问的类型,选通配置空间读数据或用户设备数据送至数据通道;三态总线驱动器对输出到用户设备的数据进行三态驱动。

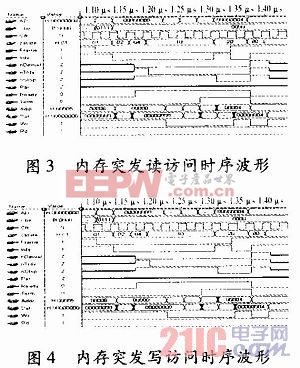

3 时序仿真

文中采用Verilog HDL语言设计实现了上述模块,在Altera公司MAX+plusIl10.0软件环境下,选用FLEX10K20RC208—3器件进行综合编译,占用341个逻辑单元,最高工作频率36 MHz,满足PCI总线的时序要求。图3是内存突发读访问的时序仿真波形,突发传输4个数据,在每个数据传输的下个时钟周期输出奇偶校验值,最后用户设备提出终止传输请求,最后一个数据传输完成后交易结束。图4是内存突发写访问的时序仿真波形,突发传输4个数据后,主设备插入等待周期,同时用户设备也有效Ready和Term请求终止传输,在第5个数据也是最后一个数据传输完成后,总线交易结束。这两个时序图属于传输最后一个数据并断开连接情形的两种不同情况。仿真波形的分析表明,从设备接口模块符合PCI规范的要求。

4 结束语

将一个FIFO模块连接到PCI从设备接口的用户总线组成测试平台,由FIFO的状态和控制信号提供同步的Ready和Term信号。这个测试平台在MAX+plusII下编译,并下载到PCI开发板上一片EPF10K20RC208-3芯片中,安装驱动程序后,PCI开发板正确识别、工作稳定、读、写数据准确无误;多组数据传输测试,测得数据突发传输率约可达到20 MB·s-1。

评论