基于SOPC的雷达多功能接口模块的设计与实现

2.2 M0子模块电路设计

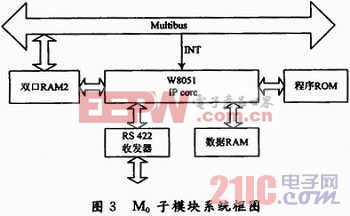

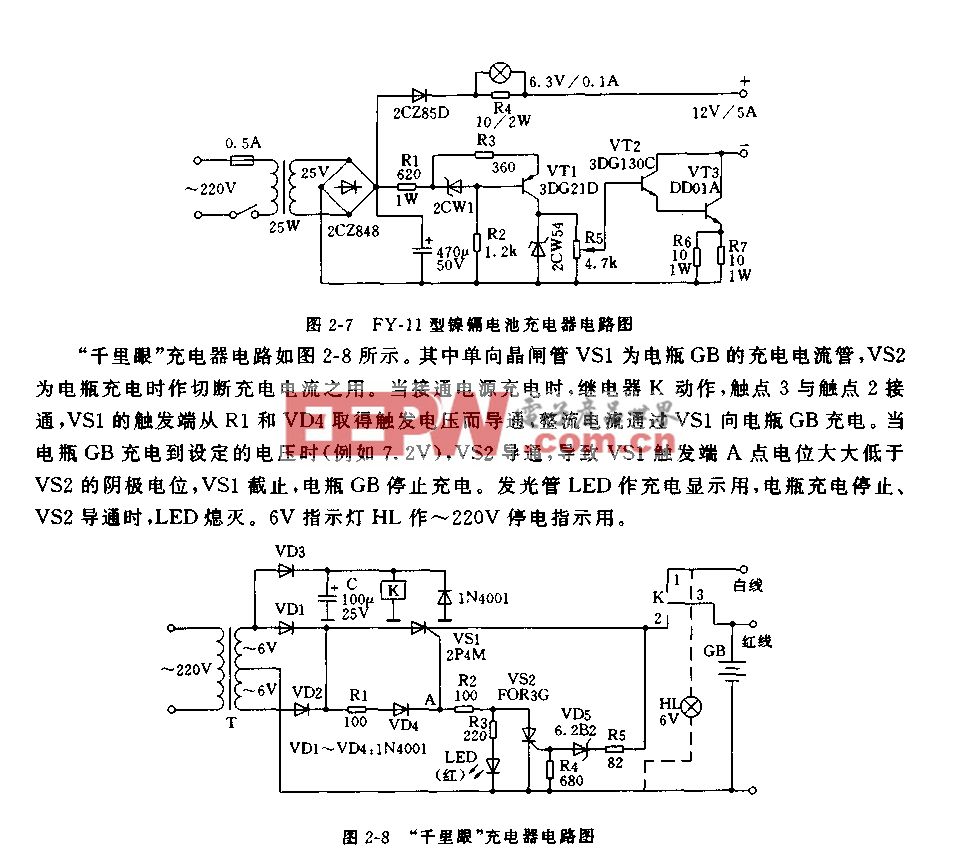

图3为内总线接口子模块(M0)系统框图,W8051是与8051单片机兼容的IP软核,它通过工作在方式2下的8051串行口实现雷达内总线M0主控器功能,分别为W8051扩展了4 KB的程序ROM和256 B的RAM,同时扩展了4 KB的双口RAM2并挂接在Multibus上,以实现与主控计算机的数据交换。主控计算机通过一个I/O(INT)来中断W8051,整个M0控制系统均在FPGA内部实现,软件在这个独立的计算机系统上实现自定义的M0内总线通信协议,以完成主控计算机与内总线上雷达其他从设备(如发射机、接收机等)的可靠通讯。本文引用地址://m.amcfsurvey.com/article/191090.htm

2.3 TVJ子模块电路设计

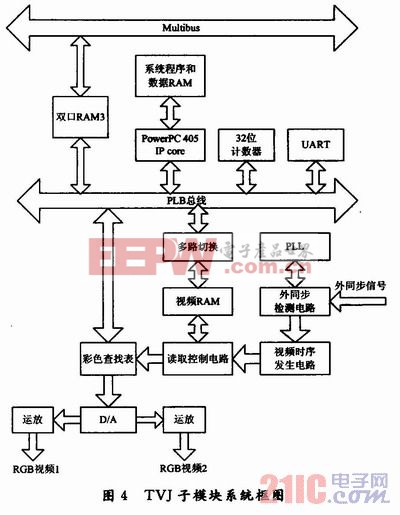

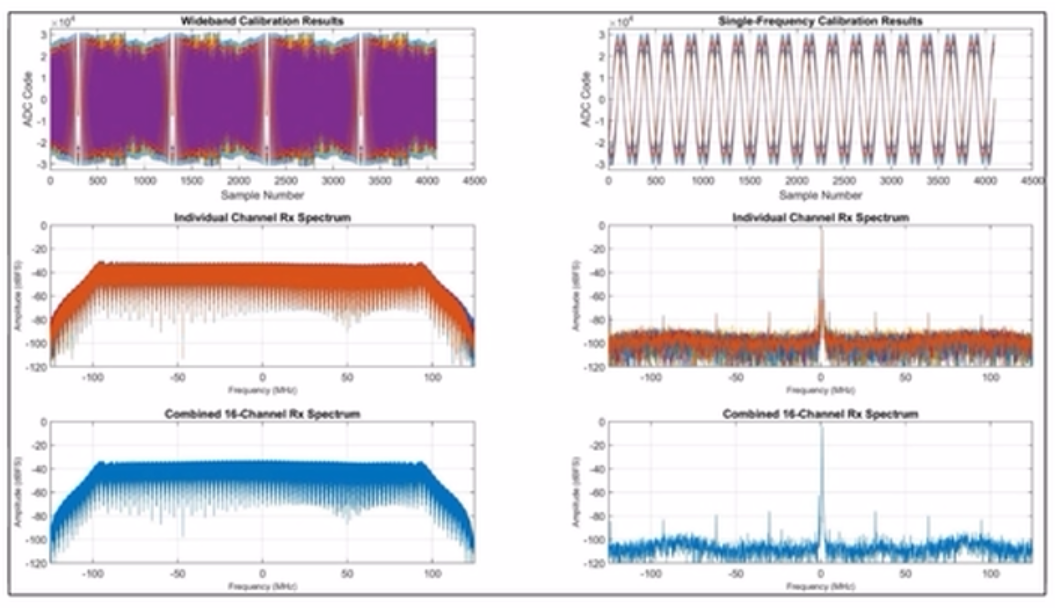

TVJ功能块的核心是基于FPGA的硬处理器核PowerPC 405,PowerPC 405是专门为嵌入式应用而设计的高性能32位PowerPC系列处理器芯核,对于Virtex-ⅡPro系列FPGA,其实现型号为PowerPC405D5,其内核的结构主要包括1个5级流水线单元,1个虚拟存储器管理单元,1个指令和数据独立的Cache单元,1个调试口和3个可编程计数器,片内总线遵循PLB(Processor Local Bus)标准,PLB是一种高性能的同步总线,用于连接处理器和高速外设,提供分离的32位地址总线和64位数据总线。通过PLB总线接口实现对视频RAM、彩色查找表LUT、32位计数器、UART和双口RAM3的扩展,在双口RAM3的另一端实现了与Multibus的存储器接口及双向中断功能,视频RAM分为A、B两块,共4 MB,显示分辨率为575×575×16 b,通过PLB总线和多路切换电路可以对它们进行读/写,同时视频RAM的内容经读取控制电路读出后经彩色查找表变换为24位真彩色数字视频再经过D/A变换和运放的驱动输出模拟视频信号。通过PLB总线可以随时设置彩色查找表LUT的内容以实时地进行多种分层叠加彩色显示方式的切换。视频时序发生电路产生符合PAL制式的同步/消隐信号,当有外部同步信号输入时,外同步检测电路可自动识别出来并与外部的锁相环(PLL)配合,产生与外同步信号完全一致的视频时序信号,保证最后输出的模拟视频与其完全同步。除去视频RAM,PLL,D/A、和运放电路外,整个PowerPC 405系统和显示控制的时序、逻辑电路及彩色查找表等都在FPGA内部实现。如图4所示。

评论