基于SOPC的雷达多功能接口模块的设计与实现

摘要:为了满足高性能和小型化的要求,采用SoPC技术在一片FPGA上实现了多个嵌入式系统来完成1553B通信和显示处理等航电接口功能,特别是用VHDL语言实现了软件可配置的彩色调色板和分层叠加显示技术,使得系统具有集成度高、配置灵活、可靠性高等优点。详细介绍了各子模块的主要功能、工作原理和关键技术,该模块已经成功应用于实际系统中。

关键词:机载雷达;FPGA;SoPC;IP核;MieroBlaze;PowerPC 405

0 引言

机载火控雷达的接口模块要承担数据处理机所有的接口任务,包括与雷达外部的航空电子系统总线、与雷达内部其他分系统(如发射机等)的通信以及输出雷达视频信号给航空电子综合显示器。这些接口功能有的比较复杂,如显示处理接口要将雷达数据处理机送来的目标、天线、航迹和地图等数据经过处理后形成符合标准的视频信号输出,有的要求高可靠性和实时性,如航电总线通信接口,而对于高性能的军用设计,又要求尽可能减小空间、功耗和重量。随着半导体工艺水平的不断发展,现场可编程门阵列(FPGA)技术也在不断进步,与1999年相比,FPGA的成本降低了500倍,逻辑容量提高了200倍,功耗降低了50倍,速度加快了40倍,并提供存储器、高速并行和串行I/O、嵌入式处理器、DSP等强大功能,使得它的应用正向更广泛的领域发展。SoPC作为一种特殊的嵌入式微处理器系统,融合了SoC和FPGA各自的优点,并具备软硬件在系统可编程、可裁减、可扩充、可升级的功能,已逐渐成为一个新兴的技术方向,采用基于SoPC的FPGA来设计嵌入式计算机系统,可以在提高系统性能的同时,将外围的数字电路模块和存储器放入芯片内设计,大大减少芯片数量,最大限度地提高系统的集成度,是目前最能满足小型化、高性能要求的新技术。本文采用Xilinx公司的基于Virtex-ⅡPro FPGA的32位软核MicroBlaze和32位PowerPC系列处理器硬核PowerPC 405。

1 应用系统和外部接口

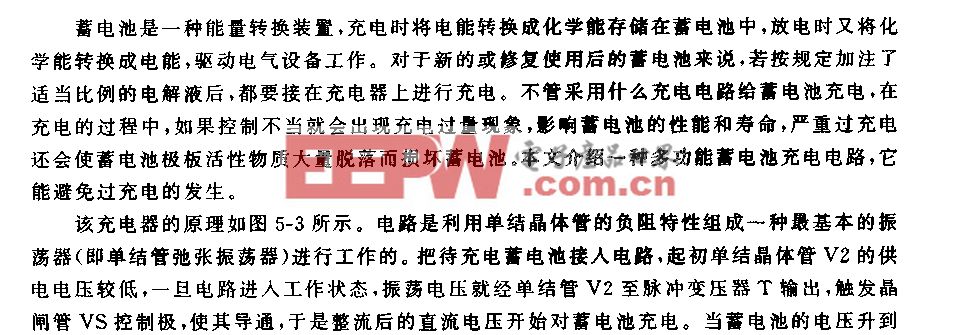

本文所设计的通用型多功能接口模块包括3个接口子模块,即与外部航电系统通信的1553B总线接口子模块(MBI)、雷达内部分系统之间的通信控制子模块(M0)和航电显示接口子模块(TVJ)。这些子模块功能彼此独立并具有实时性要求,对于MBI模块,需要系统能够实时地响应外部数据收发和高可靠性,处理速度不一定很高,对于显示控制模块,需要系统具有较高处理速度和能力以便能完成彩色雷达图像的分层叠加显示和地图画面的连续显示,针对这些要求,充分采用SoPC技术,将3个嵌入式计算机系统都放在FPGA内部设计实现,很好地满足了设计需求。图1为该系统的总体框图,3个子模块分别连接3种外部接口,同时它们通过公用的与Multibus的接口独立完成与主控计算机的数据交换。

2 系统功能和实现

2.1 MBI子模块电路设计

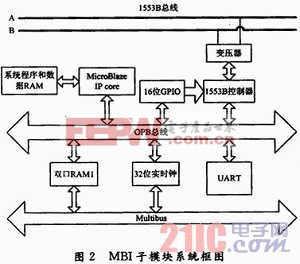

图2为1553B总线接口子模块(MBI)系统框图,Microblaze是MBI功能块的32位核心微处理器,它是一个专门为Xilinx FPGA优化的RISC嵌入式软处理器,具有32个32 b通用寄存器、硬件乘法器、32 b地址总线和32 b数据总线、三操作数32 b指令字,片内总线遵循OPB(On-chip Peripheral Bus)标准,OPB是一种完全同步总线,OPB总线接口提供分离的32位地址总线和32位数据总线。通过OPB总线实现对1553B协议芯片、32位实时钟、异步串行口(UART)、GPIO和双口RAM的扩展和控制。在双口RAM1的另一个端口设计了与Multibus的存储器接口功能,使Multibus总线和OPB总线上的主设备可同时对RAM1进行存取不会产生冲突,且可在Multibus上实现双向中断功能,此外通过Multibus的I/O接口和OPB总线接口也可以对32位雷达实时钟同时进行存取而不产生冲突。

为了可以灵活地设置1553B协议芯片的工作方式,在此通过一个OPB总线上的16位GPIO来保存和修改对芯片的工作方式的设置,它包括5位RT地址RTA[4:0],6位工作模式设置MSEL[5;0],芯片复位MRST等控制。以上电路除1553B控制器和变压器外全部都在FPGA内部用IP核和VHDL设计实现,MBI软件上电后对1553B控制器进行初始化,然后实时查询和响应雷达数据处理主机通过Multibus上的双口RAM1送来的命令和数据以及1553B总线上发来的命令,完成与其他航电设备的数据交换和通信。

评论