基于FPGA的IRTG-B码编解码器的设计与实现

摘要:为提高整个系统时间的同步精度,以便为测量设备提供可靠的时间信息和标准频率信号,给出了一种基于FPGA的IRIG-B编解码器的设计与实现方法。新系统基于模块化设计,其中编码部分完成标准时间信息及相应的BCD码的产生,并在标准时间BCD码中加入帧开始标志位、位置识别标志和索引标志识别,从而将BCD格式的时间信息变成IRIG-B格式码,同时数据并串处理可通过FPGA的一个I/O端口发送串行数据。解码部分则完成串行IRIG-B格式码的接收并判断帧开始标志位和位置识别标志,再解出相应原始时间信息并存储到双端口的RAM中,最后以并行方式输出。

关键词:IRIG-B;可编程逻辑器件;FPGA;编码器;解码器

0 引言

时间统一(以下简称时统)系统是武器系统试验测试、通信、气象、航天、工业控制、电力系统测量与保护等领域的关键技术,主要为其他参试测试设备提供标准时间信号和标准频率信号。随着现代信息技术的不断发展,对标准化时间系统设备的要求越来越高,IRIG-B码以其优越性成为时间系统设备的首选。而对信号的帧结构的可编程度、集成度的需求越来越高,用于时间系统的IRIG-B码源的设计也趋于高度集成化。FPGA可编程逻辑器件的规模比较大,适合于时序、组合等逻辑电路应用场合,同时具有实时性好、可靠性高、成本低、可编程等优势。本文介绍了采用Ahera公司的EP20K200E器件所设计的IRIG-B时统信号发生及解码电路。

IRIG-B编码模块主要利用外部时钟脉冲信号来触发,它将用于产生IRIG-B码的各种门电路集成在一个芯片,以产生标准的IRIG-B串行时间码并向设备终端发送,从而完成DC码编码。通过设备终端对接收到的IRIG-B码进行解调,便能产生出系统所需的标准时间和各种控制信号,然后再存储到相应的双端口RAM中。

1 系统整体硬件设计

IRIG(Inter-Range Instrumentation Group)是美国靶场司令部委员会的下属机构,称为“靶场时间组”。IRIG-B码(DC)以其实际的优越性能而成为时统设备最佳选择的标准码型。IRIG时间标准有两大类:一类是并行时间码格式,这类码由于是并行格式,传输距离较近,且是二进制,因此远不如串行格式广泛;另一类是串行时间码,共有六种格式,即A、B、D、E、G、H。它们的主要差别是时间码的帧速率不同,B码的主要特点是时帧速率为1帧/s;而且携带信息量大,经译码后可获得1、10、100、1000 c/s的脉冲信号和BCD编码的时间信息及控制功能信息;此外,B码的分辨率高,调制后的B码带宽能适用于远距离传输,它分为直流、交流两种,而且接口标准化,国际通用。

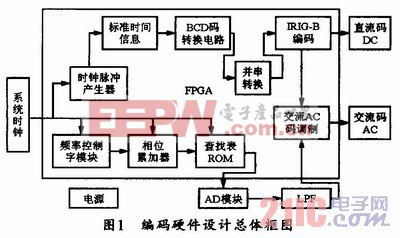

IRIG-B码编码器由时钟脉冲发生器模块、标准时间形成模块、BCD码转换模块、并串转换、直流码形成模块和交流码模块组成,其编码器硬件设计总体框图如图1所示。

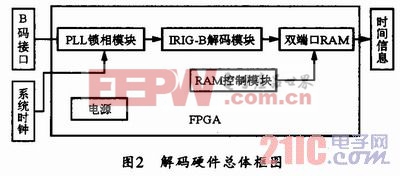

IRIG-B解码器则由锁相环PLL模块、IRIG-B解码模块、双端口RAM、RAM控制模块等组成。其解码硬件的设计框图如图2所示。

评论