基于FPGA的雷达中/视频数据采集与回放系统设计

0 引言

随着科学技术的飞速发展,在军事、航空航天和测试及测量等领域,人们对数据采集系统的采样精度、采样率和存储量等指标提出了更高的要求。传统的采集器件使用起来很不方便,其局限性非常明显,显然已经不能适应现代技术发展的需要。目前,随着集成电路技术的进步,大规模和超大规模的可编程逻辑器件在实际系统设计中得到广泛的应用。由于其集成度高、功耗低、设计灵活、效率高等优势,同时器件具有用户可编程特性,可大大缩短系统设计周期,减少设计费用,降低风险投入,而且部分器件还具有在线可编程的能力。

在此介绍一种雷达中/视频数据采集记录系统,它的核心技术是利用高速可编程逻辑门阵列FPGA对雷达目标回波进行高速实时采集,并将持续采集来的信号数据记录在计算机硬盘上,以供后续数据处理需要。本系统的特点是:小型化,便于携带,连接方便,操作简单,记录时间长,采样率高,数据传输率高,动态范围大(12位A/D分辨率),并采用正交双通道采集方式,完全符合高速大容量雷达信号采集记录的需要。

1 系统组成与工作原理

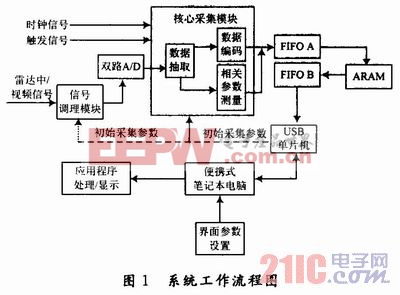

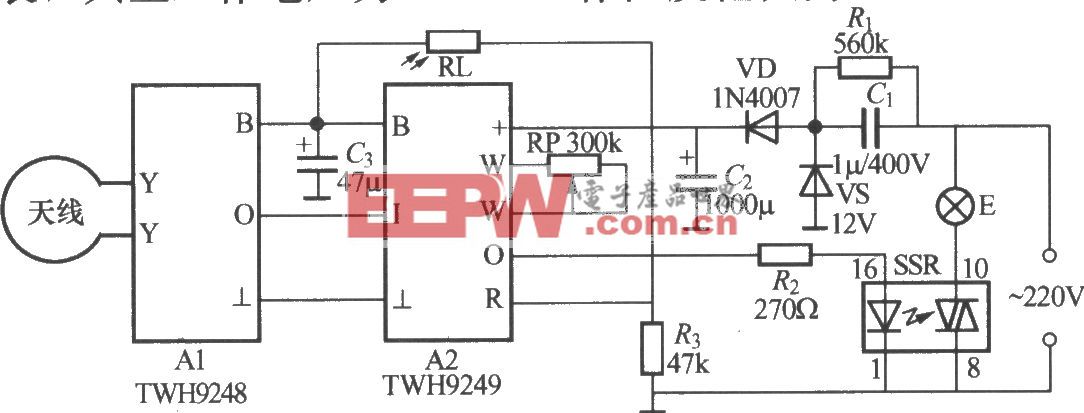

系统主要由计算机和系统采集硬件组成,系统采集硬件由一块带有双路高速A/D和USB接口电路的底板和一块带有FPGA的核心板组成。雷达数据采集记录系统的工作流程如图1所示。

系统以台式PC作为采集主控设备,雷达中/视频回波信号经A/D转换器进行模数转换,再由FPGA控制的核心采集模块来完成数据的采集量化,采集模块可以根据来自雷达系统的时钟、同步触发信号来控制对雷达回波信号的采集,然后将采集到的数据通过缓冲模块送给USB,USB接口将数据打包传送到台式电脑的硬盘上以供显示和处理使用。

FPGA与上位机间的数据交换是实现系统功能的重要一环。一方面,FPGA在完成对采集数据的抽取和缓冲后,采用高速的USB 2.0传输方式将数据实时地传输给上位机,使数据处理能够顺序进行;另一方面,数据采集模块的某些参数由上位机控制面板设置后经总线传送给FP-GA。

2 硬件电路板设计

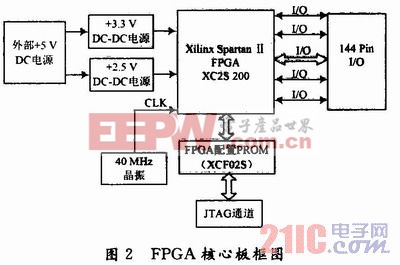

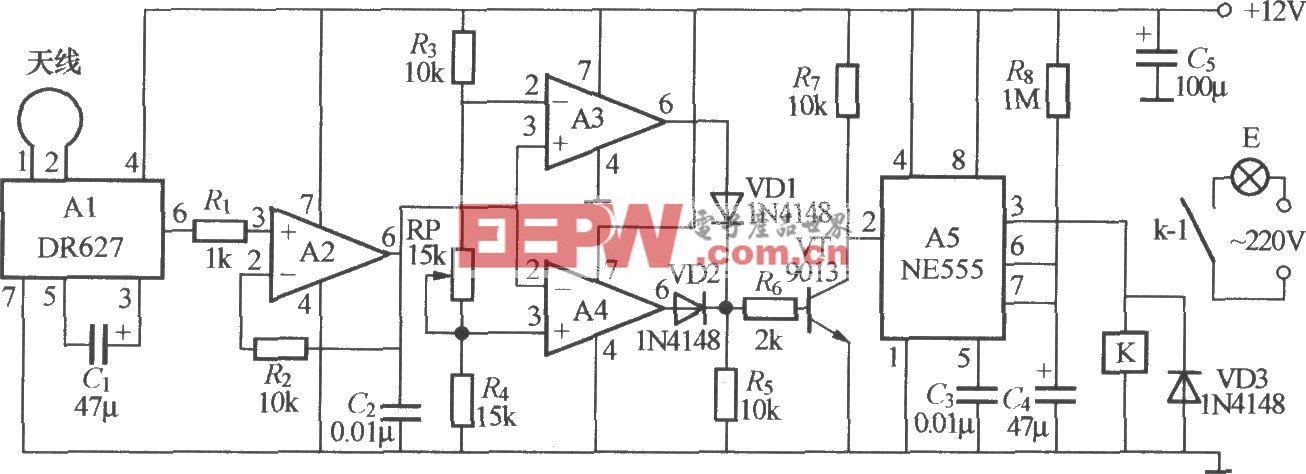

在本系统中,FPGA核心板担负着数据存储,数据传输控制的任务,是本系统最为关键的部分,综合考虑系统资源和FPGA价格,选择Xi-linx公司的Spartan-Ⅱ系列XC2S200芯片较为适宜,由电源转换芯片LT1764为FPGA提供稳定的电源电压。其最小系统框图如图2所示。

XC2S200是推出的性价比更好的Spartan-Ⅱ系列FPGA产品中的一款,有着成熟的Virtex-E架构,内核电压采用1.8 V,系统性能可达到200 MHz,系统门数为200 000系统门,内部包括适量的分块RAM(Block-RAM)。该芯片支持丰富的接口标准。本系统采用ADI公司的AD9224为A/D转换芯片,完成双路A/D采样功能。其采样频率为40 MHz,采用位数达12位,片内集成高性能的采样保持放大器和参考电压源,具有纠正错误输出的逻辑功能,精确提供了在40 MSPS采样率下12位的输出数据,保证在完全可以运作的温度范围内无漏码。

高速的数据采集速度是保证数据采集精度的标准,但往往在数据处理时并不需要以同样的速度来进行,否则对硬件的需求太高,成本也较高。这里采用同步FIFO、SRAM、异步FIFO相结合的方法实现了对采集数据的缓冲处理。同时,由于数据的传输速度大于AD的采样速度,保证了采集的数据在传输时无遗漏。

3 软件设计

3.1 FPGA程序设计

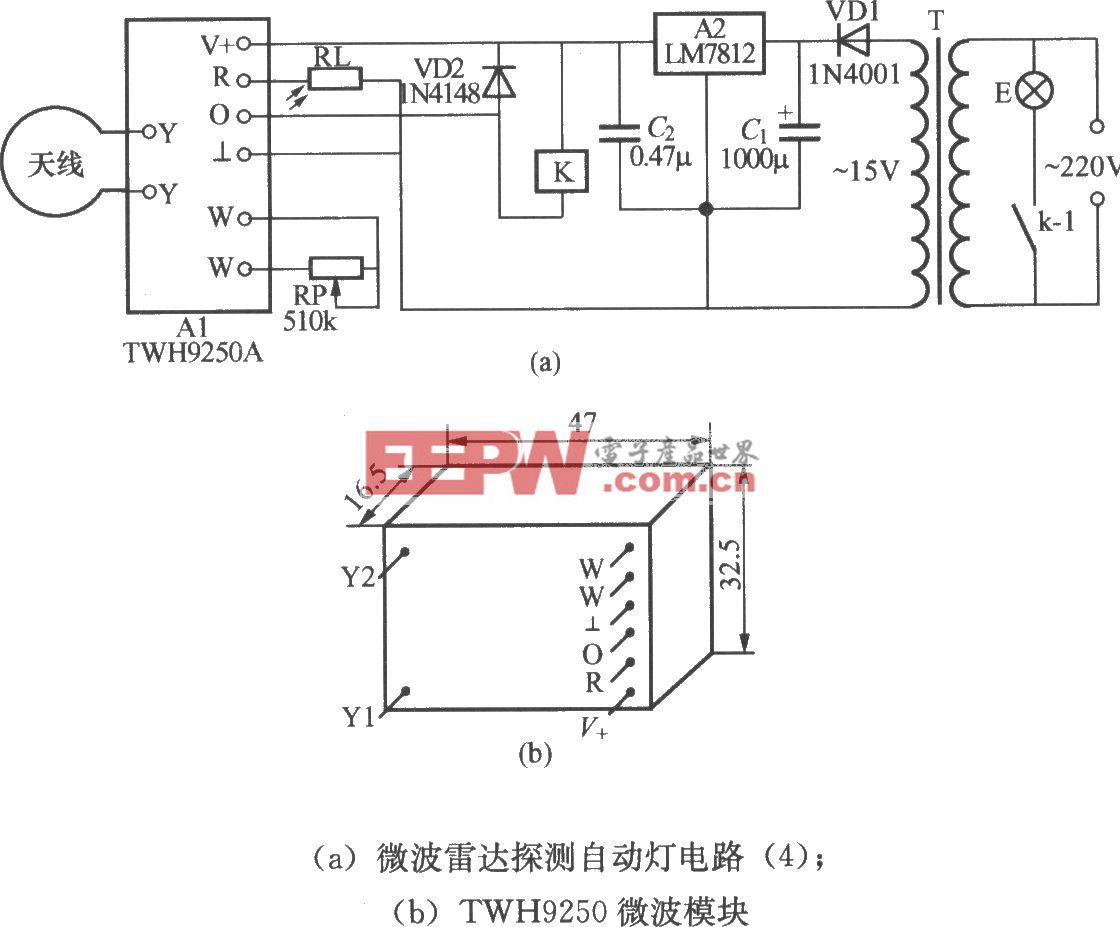

本系统采用了同步FIFO A、异步FIFO B和缓冲SRAM相结合的设计方法,共同构成本系统的数据缓冲模块。整个系统的详细设计流程如图3所示。

评论