一种全新的深亚微米IC设计方法

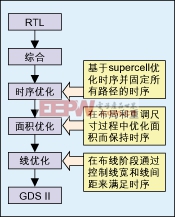

在进行IC设计过程中,最重要的就是怎样快速从RTL得到GDSⅡ。利用Logical Effort理论,我们将建立新的IC设计方法。

首先对综合库进行分析。库可以是.lib、LEF、GDSⅡ等。库中每个功能的cell会有不同的尺寸表示不同的驱动能力。我们将为这一族cell建立一个抽象cell,叫做supercell。这个supercell有固定的本征延迟和可变的大小。在对库进行分析时,我们会给supercell的延迟再加上一个可变延迟。可变延迟依赖门的负载。通常库分析得到的可变延迟是每个cell驱动它的完美负载得到的延迟,也叫做理想可变延迟。

supercell库建好之后,利用这个库和RTL代码、设计限制等就可以进行综合了。综合的关键部分就是创建好的逻辑结构。任何设计都有许多种功能正确的电路结构。综合算法的目标是发现最好的电路结构来满足时序目标。时序优化过程就是使每个可变延迟尽可能靠近它的理想可变延迟。

例如一个非常简单的库,仅仅由五个基本逻辑门组成:反向器、两输入的AND、NAND、OR和NOR门。让我们进一步假设反向器有8个版本,而其它的门有4个版本,不同的版本表示不同的尺寸,能提供不同的驱动能力。现在我们考虑一个简单功能的RTL表示,例如w=!((!x+y)Z)。这个功能可以用不同的逻辑门拓扑结构来实现,如图2所示的三种结构。

利用supercell代替库中的门,gain-based的综合只需要快速评估a、b、c三个结构,gain等于1的结构就能提供最好的时序解决方案,而传统的方法对于电路a就有128种选择。因此gain-based的综合时间将大大减少,并且非常简单,比传统的综合方法有更大的处理容量。

延迟计算就是利用上一节的gain-based的方法。基于supercell,时序优化设计完成之后,然后固定时序,使得接下来的布局布线与逻辑综合操作在同一平面内。

综合之后,设计进入到size-driven布局、load-driven布线阶段。这个时候是supercell真正表演的时候。首先利用supercell来布局,同时确保指定的时序保持常数。必要的时候插入buffer,并且时钟、电源布线开始。线的负载是基于网的全局布线结构来决定。基于每个supercell看到的实际负载,动态调整supercell的大小来满足时序预算。supercell的大小调整好之后,就把supercell用库中有适当驱动能力的cell来代替。这里关键的一点就是最小可能大小的门被选取来满足时序预算。结果芯片不再臃肿。因而会减少空间竞争,减少功耗和信号完整性问题。

最后利用详细的布线工具来调整线宽和线的间距,以保持原始的时序预算,并且确保信号完整。当然,在整个物理综合过程中,我们也会利用DRC、ERC、LVS等工具来验证各个阶段的版图,也会利用参数提取工具在各个阶段来提取参数,为supercell的大小调整以及supercell的gain调整提供信息。

利用supercell技术,从RTL到GDSⅡ的实现的几个主要步骤见图3。

这就是基于Logical Effort理论的新设计方法,特别适合于设计快速的CMOS电路。在这里我们只简单描述了它的设计思想。由于只是初步研究,肯定会有很多错误和问题,欢迎大家指出并讨论。

评论