基于模块化设计方法实现FPGA动态部分重构

配置列根据分配给它的配置地址(Configuration Address)来寻址。每一个配置列在FPGA内都有唯一的主地址(Major Address)空间。

FPGA的逻辑功能通过配置比特流(Configuration Bitstream)来实现。对于动态部分重构功能来说,需重构的配置逻辑是通过下载不同的部分配置比特流来实现的。

所谓的FPGA模块化设计就是将系统按照一定规则划分成若干模块,然后对每个模块分别进行设计、综合,并将实现结果约束在预先设置好的区域内,最后将所有模块的实现结果有机的组织起来完成整个系统的设计[4]。其划分模块的基本原则为:子模块功能相对独立,模块内部联系尽量紧密,模块间的连接尽量简单。对于那些难以满足模块划分准则的具有强内部关联的设计,不适合采用此设计方法。

FPGA模块化设计的优点在于:团队式并行工作从而加速整个项目的开发进度;每个子模块都能够灵活使用综合和实现工具独立进行优化,从而达到更好的优化结果;调试、更改某个子模块时,不会影响其他模块的实现结果,保证了整个设计的稳定性与可靠性。

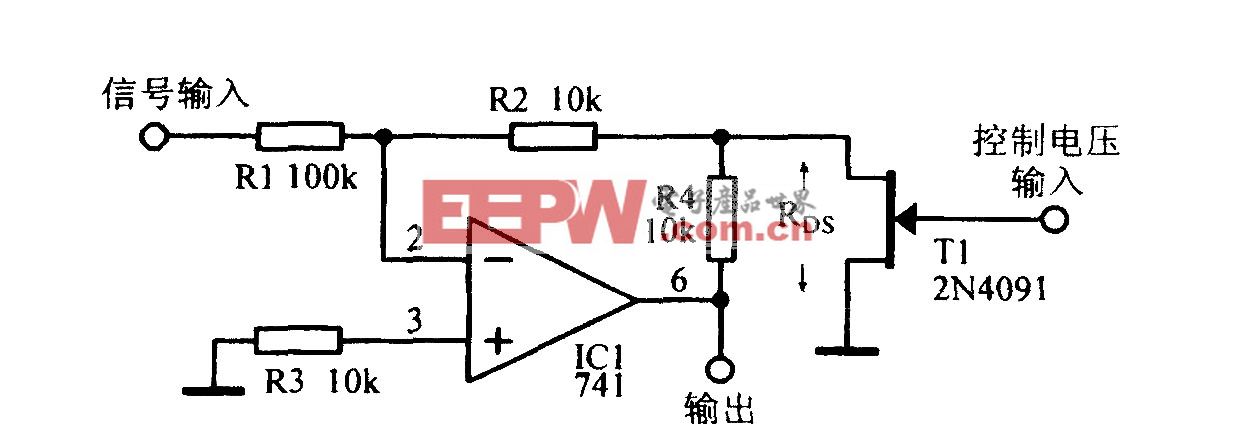

模块化设计方法使用Xilinx公司的ISE软件设计工具,常用HDL语言作为设计输入,顶层模块描述设计的全局逻辑,包括设计的输入/输出、所有子模块的黑盒子(Black Box)声明以及子模块之间的连接关系。所谓黑盒子声明是指在顶层模块中仅仅对子模块进行端口描述与信号属性声明,并不包含任何实际逻辑和时序关系的描述。子模块通常也使用HDL语言描述,分别设计出各子模块的逻辑实体并综合所设计的子模块。由于子模块的输入/输出并不是整个设计的外部接口,所以在综合过程中应禁止子模块插入I/O端口,而仅在综合顶层模块时才插入I/O端口。最后将所有子模块的实现结果和顶层的实现结果有机地组织起立,完成整个设计的实现。图2是基于模块化设计方法的流程。

采用模块化设计方法实现FPGA的动态部分重构,首先进行模块划分,将设计的固定逻辑即运行过程中不需要更改的逻辑划分到固定模块,将需要更改的部分划分到可重构模块中。其次模块的放置位置和大小也有限制,必须遵循一定的规则[5]:可重构模块的高度和器件的高度一致,从图1中可以直观地认为模块必须包含整个配置列;可重构模块的宽度最小是4个Slice(一个CLB包含两个完全相同的Slice),并且必须为4个Slice的倍数;如果可重构模块位于器件的最左边或是最右边的Slice列,则所有位于器件边缘的IOBs将作为可重构模块的资源;为了减少设计的复杂度,可重构模块的数量应该尽量少等。

图2 模块化设计流程

3 FPGA动态部分重构的实现

在本设计实例中,FPGA实现的功能是对外围接口电路进行逻辑控制以及根据外围不同设备输入的数据选择适当的数据处理算法。据此将设计划分为固定模块和可重构模块,其中固定模块内实现对外接口的控制逻辑,可重构模块内实现数据处理算法。本例中只将FPGA的逻辑功能更换一次,即可重构模块只部分重构一次,将其在重构前后的不同逻辑功能分别计作reconfig_a和reconfig_b。系统会根据需要动态部分重构FPGA,为不同的数据源选择适合的处理方法。本设计由Virtex-E XCV600E器件来实现。

根据模块所需资源的大小和模块划分原则,在用户约束文件(UCF)中将每个模块的位置进行约束,如下所示:

INST fix AREA_GROUP = AG_fix ;(1)

AREA_GROUP AG_fix RANGE = CLB_R1C1:CLB_R48C36 ;(2)

INST reconfig AREA_GROUP = AG_reconfig ; (3)

AREA_GROUP AG_reconfig RANGE = CLB_R1C37:CLB_R48C72 ;(4)

其中(2)、(4)指定了两个模块的具体位置。

评论