基于FPGA的UART设计与实现

比较而言,UART发送器的设计相对容易,只要每隔一个发送周期并按照数据帧格式输出数据即可,本文将对接收器的设计和实现做详细说明,发送器的设计方法基本相同。

接收器的工作过程如下,在接收数据寄存器被读出一帧数据或系统开始工作以后,接收进程被启动。接收进程启动之后,检测起始位,检测到有效起始位后,以约定波特率的时钟开始接收数据,根据数据位数的约定,计数器统计接收位数。一帧数据接收完毕之后,如果使用了奇偶校验,则检测校验位,如无误则接收停止位。停止位接收完毕后,将接收数据转存到数据寄存器中。

为确保接收器可靠工作,在接收端开始接收数据位之前,处于搜索状态,这时接收端以16倍波特率的速率读取线路状态,检测线路上出现低电平的时刻。因为异步传输的特点是以起始位为基准同步的。然而,通信线上的噪音也极有可能使传号“1”跳变到空号“0”。所以接收器以16倍的波特率对这种跳变进行检测,直至在连续8个接收时钟以后采样值仍然是低电平,才认为是一个真正的起始位,而不是噪音引起的,其中若有一次采样得到的为高电平则认为起始信号无效,返回初始状态重新等待起始信号的到来。找到起始位以后,就开始接收数据,最可靠的接收应该是接收时钟的出现时刻正好对着数据位的中央。由于在起始位检测时,已使时钟对准了位中央,用16倍波特率的时钟作为接收时钟,就是为了确保在位宽的中心时间对接收的位序列进行可靠采样,当采样计数器计数结束后所有数据位都已经输入完成。最后对停止位的高电平进行检测,若正确检测到高电平,说明本帧的各位正确接收完毕,将数据转存到数据寄存器中,否则出错。本文引用地址://m.amcfsurvey.com/article/191633.htm

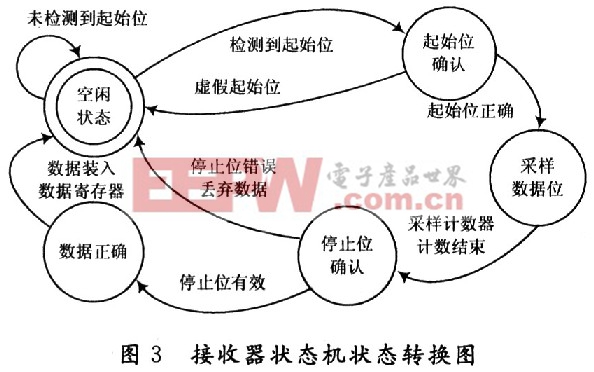

采用有限状态机模型可以更清晰明确地描述接收器的功能,便于代码实现。接收器的状态转换图如图3所示,为突出主要过程,图中省略了奇偶校验的情况。接收器状态机由5个工作状态组成,分别是空闲状态、起始位确认、采样数据位、停止位确认和数据正确,触发状态转换的事件和在各个状态执行的动作见图中的文字说明。

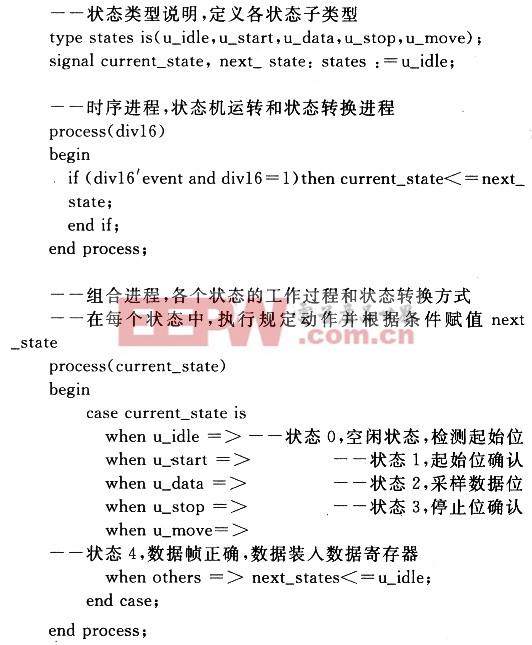

在状态机模型的基础上,使用VHDL来描述接收器功能,其主要代码如下:

实现用16倍波特率时钟确定起始位的具体方法是设计两个输入数据位寄存器rxd1和rxd2,使用语句“rxd1=rxd;rxd2=rxd1;”接收数据并进行判断。当检测到rxdl=O并且rxd2=1时可以确定下降沿发生,连续7个时钟rxd2=0即确定检测到起始位,之后为了确保在数据位中央接收数据,同样用16倍波特率时钟对数据位进行采样。接收数据的方法是设计一个寄存器rxd_buf(7 downto 0),用语句“rxd_buf(7)=rxd2;rxd_buf(6 DOWNTO 0)=rxd_buf(7 DOWNTO 1);”实现移位寄存器右移操作,执行8次后接收到一个完整数据。

1.3 波特率发生器设计

波特率发生器实质是设计一个分频器,用于产生和RS 232通信同步的时钟。在系统中用一个计数器来完成这个功能,分频系数N决定了波特率的数值。该计数器一般工作在一个频率较高的系统时钟下,当计数到N/2时将输出置为高电平,再计数到N/2的数值后将输出置为低电平,如此反复即可得到占空比50%的波特率时钟,具体的波特率依赖于所使用的系统时钟频率和N的大小。如系统时钟频率是40 MHz,要求波特率是9 600,则16倍波特率时钟的周期约等于260个系统时钟周期,则计数器取260/2=130时,当计数溢出时输出电平取反就可以得到16倍约定波特率的时钟。

使用VHDL来描述波特率发生器的完整代码如下:

评论