基于FPGA的UART设计与实现

2 数据传输测试

随着逻辑设计复杂性的不断增加,仅依赖于软件方式的仿真测试来了解系统的硬件功能有很多的局限性,应用QuartusⅡ集成开发环境中提供的SignalTapⅡ嵌入式逻辑分析仪,可以将测试信息随设计文件下载于目标芯片中,用以捕获目标芯片内部系统信号节点处的信息或总线上的数据流,而又不影响原硬件系统的正常工作。测试信息通过器件的JTAG端口传出,并送入计算机进行显示和分析,这是一种高效的硬件测试手段,并很好地结合了传统的系统测试方法。

本设计在Altera Cyclone系列的EPlC6Q240C8芯片上进行了验证,使用QuarltusⅡ软件将编译好的.pof格式文件以AS模式下载到配置芯片EPCS1中。在计算机端运行串口调试助手软件,将数据从计算机送出,并利用FPGA上的UART模块进行接收,将发送数据与SignalTapⅡ获取的波形进行对比,经多次测试表明收发数据完全相同。本文引用地址://m.amcfsurvey.com/article/191633.htm

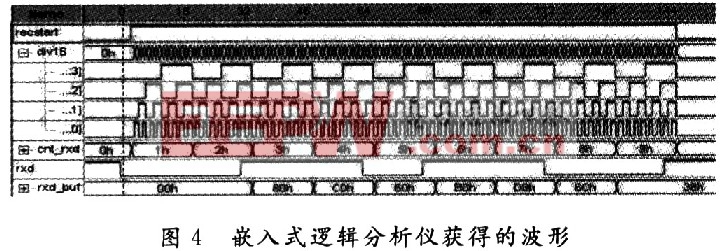

以其中一次的测试为例进行说明,从PC上输入ASCII码的“6”,设定波特率发生器时钟作为SignalTapⅡ的采样时钟,采样波形如图4所示,其中“recstart”表示开始接收数据帧标志;“divl6”表示16倍波特率时钟;“cnt_rxd”表示数据位采样计数器,一次完整的采样计数从Oh~9h共10次采样(1个起始位,8个数据位,1个停止位);“rxd”表示串口的接收端;“rxd_buf”表示移位寄存器,当数据停止位确认后,移位寄存器输出收到的数据“36h”,表明了该UART工作稳定可靠。

应特别注意的是当利用SignalTapⅡ进行测试工作结束后,在生成最终产品前,应将SignalTapⅡ从芯片中除去,以免占用额外的资源,然后再重新编译下载。全程编译后报告消耗逻辑单元142个,只占芯片总资源的2%,没有占用芯片的存储单元和PLL单元,对于一个中大规模的FPGA芯片而言这是非常少的资源消耗。

3 结语

基于FPGA设计和实现UART,可以用片上很少的逻辑单元实现UART的基本功能。与传统设计相比,能有效减少系统的PCB面积,降低系统的功耗,提高设计的稳定性和可靠性,并可方便地进行系统升级和移植。

本设计具有较大的灵活性,通过调整波特率发生器的分频参数,就可以使其工作在不同的频率。采用16倍波特率的采样时钟,可以实时有效探测数据的起始位,并可对数据位进行“对准”中央采样,保证了所采样数据的正确性。该模块可以作为一个完整的IP核移植进各种FPGA中,在实际应用时可嵌入到其他系统中,很容易实现和远端上位机的异步通信。

评论