基于FPGA的增量型光电编码器抗抖动二倍频电路设计

2.2.1 滤除编码器抖动的原理

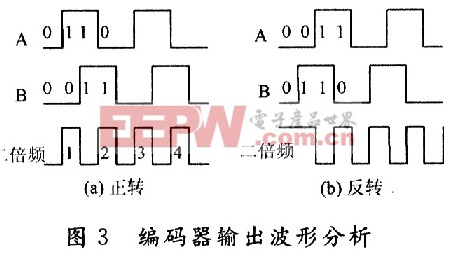

采用二倍频技术滤除抖动脉冲。所谓二倍频技术即对A相或者B相每个脉冲的上升沿和下降沿分别计数。光电编码器经过二倍频后正常输出波形如图3所示,A相脉冲O→1跳变时,B为O,则编码器正转;B为1,则编码器反转。A相脉冲1→O跳变时,B为1,则编码器正转;B为0,则编码器反转。编码器正常输出波形时,A、B两相交替跳变,如果A相发生跳变后,B相没有发生跳变A相又发生跳变,此时认为是干扰脉冲,反之同样视为干扰脉冲。本文引用地址://m.amcfsurvey.com/article/191645.htm

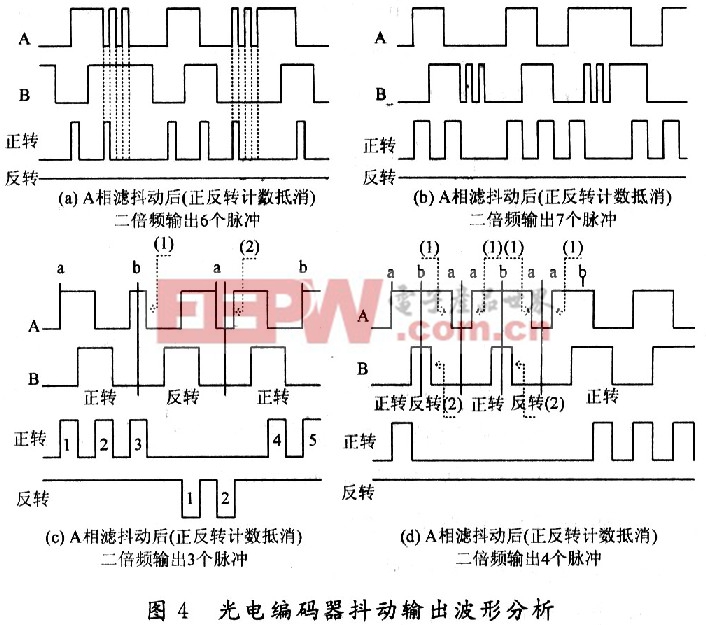

分析图4,对A相的跳变沿进行二倍频计数,B相的高低电平用来判断编码器的正反转。B相边沿的抖动脉冲对二倍频计数没有影响,如图4(b)所示。分析图4(a),A相边缘的抖动认为是干扰脉冲被滤除掉。图4(c),图4(d)中的a,b标记的位置是编码器物理地址,如图4(d)标记的a,b表示编码器在此处反复振动。图4(c)、图4(d)(1)、(2)标记处跳变沿视为抖动脉冲,应滤除,A相的正转脉冲数据数和反转脉冲数据数相减后就是A相实际二倍频后的脉冲数据。

2.2.2FPGA滤除编码器抖动及仿真结果

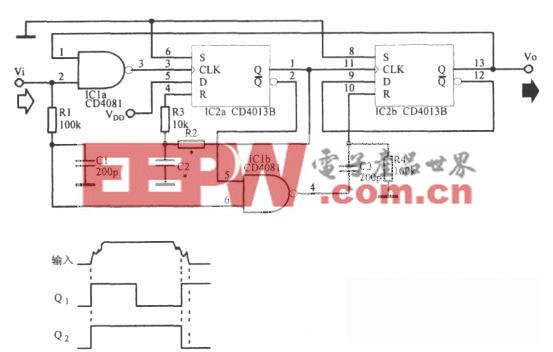

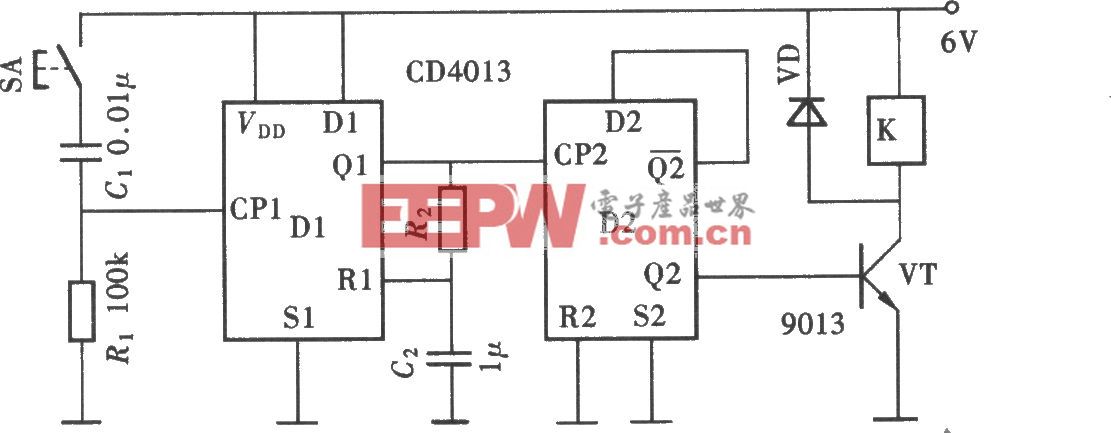

根据以上分析,本文采用FPGA滤除增量型光电编码器输出抖动脉冲。编译环境采用QuartusⅡ8.O。在FPGA中使用图形和语言结合的方法设计逻辑模块。内部的逻辑子模块采用Verilog语言来实现。顶层模块的结构图如图5所示。A和B输入引脚连接增量型编码器A相和B相信号。Acount为16位的数据寄存器,输出当前编码器的位置。顶层设计中包含两个模块,一个是根据编码器的B相跳变沿记录来滤除编码器A相抖动脉冲的BlockA模块,该模块根据滤除后的A相脉冲数据个数并记录脉冲数据。Verilog的主要程序如下:

评论