基于FPGA的增量型光电编码器抗抖动二倍频电路设计

本文引用地址://m.amcfsurvey.com/article/191645.htm

本文引用地址://m.amcfsurvey.com/article/191645.htm

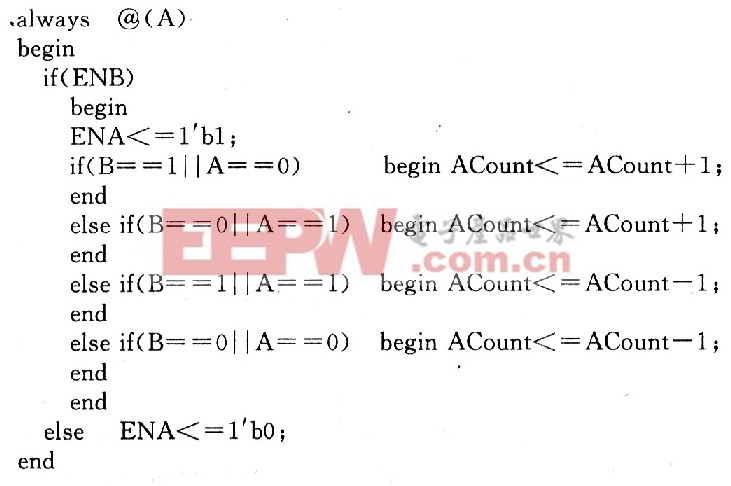

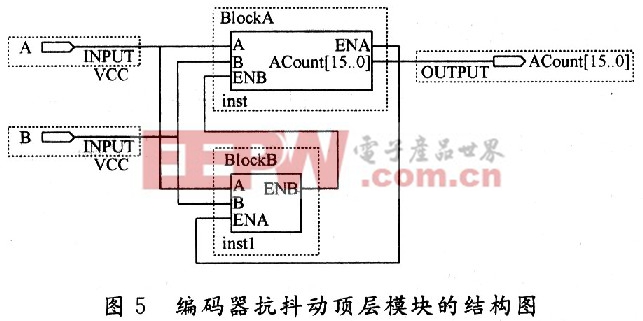

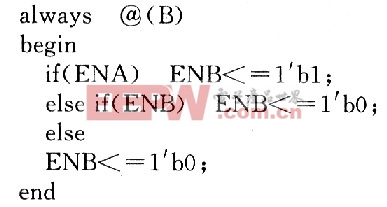

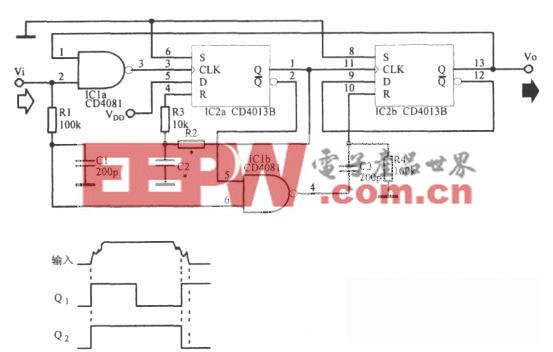

另一个模块BlockB主要完成的功能是滤除编码器B相的抖动脉冲。根据分析滤除编码器抖动的原理,ENA引脚为BlockA模块的输出引脚,当A相输入引脚有跳变时ENA为1,A相引脚有连续的跳变或者接下来B相有跳变时ENA为0。ENB为编码器B相跳变使能引脚,当ENA为1时如果B相有跳变ENB为1,当ENA为1时如果B相有连续跳变ENB为0。主要程序如下:

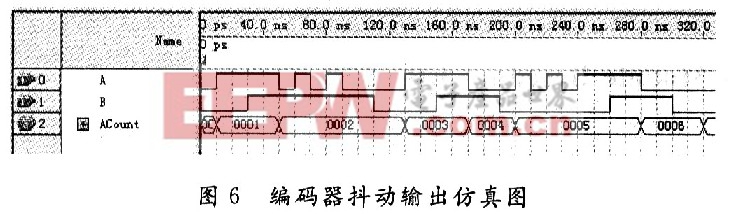

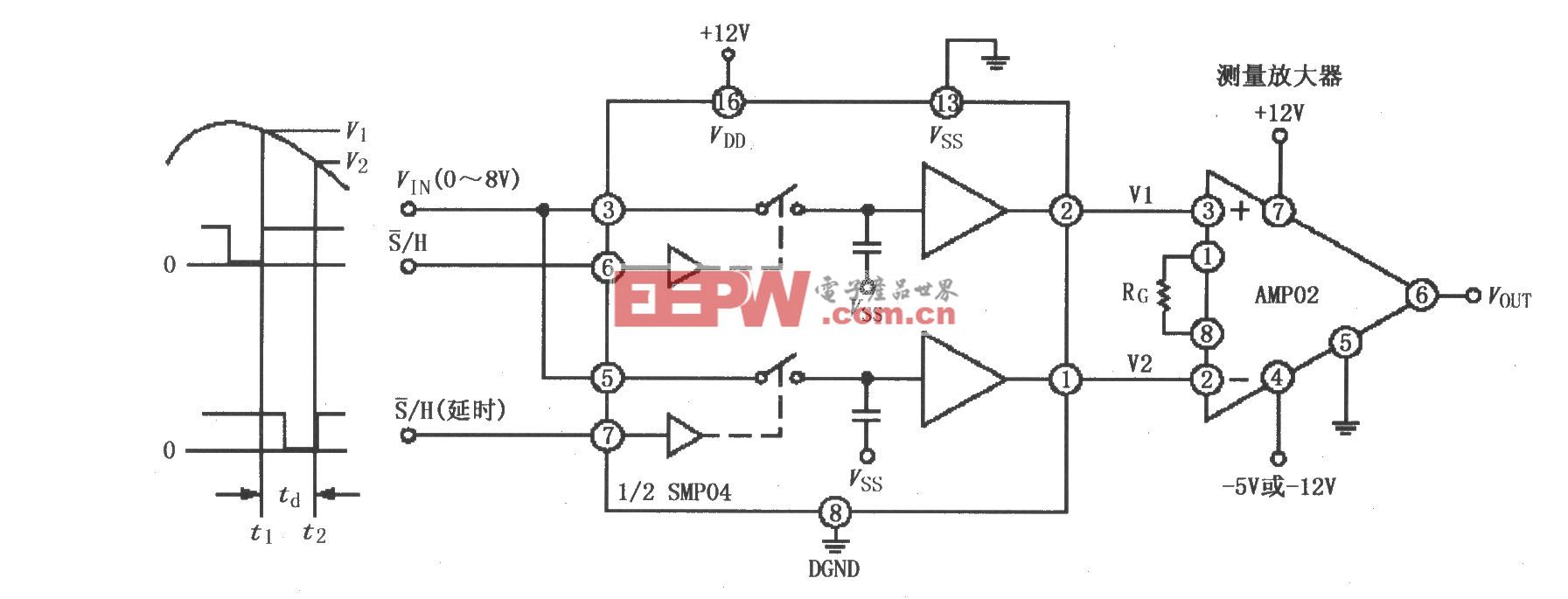

以图4(a)的编码器抖动输出仿真为例,仿真效果如图6所示。从图中分析,A相输出7个脉冲,应该输出3个脉冲,二倍频后是14个脉冲,应该输出6个脉冲,经过滤除后脉冲计数器数为6个。A相的抖动脉冲得到有效的滤除。

3 结语

现场调试结果证明,该算法可以消除工业现场出现的干扰和抖动现象,能够准确地记录脉冲数据。此滤波方法可以采用软件滤波,但是软件滤波需要的引脚较多,采用两个中断引脚响应A相的上升沿和下降沿,浪费CPU资源。采用FPGA实现编码器的滤波,设计方便,改动灵活。

评论