基于FPGA的超声波气体流量计中AGC的实现

3 数字AGC的设计

数字AGC系统组成包括A/D转换器(ADC)、现场可编程门阵列(FPGA)、可编程只读存储器(PROM),如图2所示。

3.1FPGA选型简介

该设计采用Altera公司的ACEX系列FPGA器件EPlK30TCl44-3作为核心控制器,其特点是:高密集型;适合大容量应用的低成本可编程结构;多电平标准系统,其I/O接口可驱动2.5 V和3.3 v器件或被5 V器件驱动;灵活的内部连接;强大的I/0接口.对于每个I/0接口有独立的三态输出控制使能,对于每个I/O接口都有开漏输出选择。

EPIK30TCl44-3型FPGA满足该系统设计要求,30 000个逻辑门适合于数字系统设计所需的逻辑门数量;多电平标准简化了FPGA与外部电路的接口;102个功能强大的I/0接口方便了FPGA外嗣电路设计;JATG边界扫描功能为系统开发与完善提供了很大的方便。

3.2 FPGA内部设计

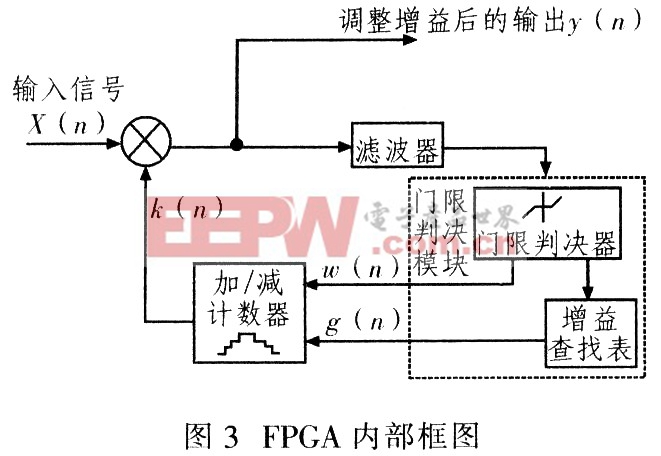

该设计主要由乘法器、门限判决、寄存器、加/减计数器4个模块组成,实现40 dB动态范围的控制。FPGA内部框图如图3所示。

经A/D采样后的信号x(n)进入FPGA进行处理。x(n)首先进入乘法器模块与可控增益因子k(n)相乘,然后分成两路。一路作为调整增益后的AGC输出y(n);另一路送入门限判决模块。门限判别模块包括门限判决器和增益查找表,门限判决器内设有高低2个门限,当输入包络信号电平大于高门限时,则认为输入信号过大,应调整增益控制因子k(n)减小:当输入包络信号电平小于低门限时,则认为输入信号过小,应调整增益控制因子k(n)增加。对于增加或减少的步进量g(n)则从增益查找表中得到。加/减计数器模块根据查找表得到的步进因子g(n)及门限判决模块提供的计数方向w(n)来调整增益控制因子的。

3.2.1 门限判决模块

门限判决模块用于限制加/减计数器控制号的波动,防止环路振荡,其内设高低2个门之间的范围即为AGC输出信号的波动范围。防止AGC发生振荡,该范围应该在满足解调器要求的动态范围条件下足够宽,而不是恒定不变的电平值。如果大于高门限,则认为信号过大,首先送给加/减计数器一个向下计数的信号,然后根据信号的范同从查找表中确定加/减计数器的步进量;如果小于低门限,则认为信号过小,首先送给加/减计数器一个向上计数的信号,然后根据信号的范围从查找表中确定加/减计数器的步进量;如果在两门限之间,则加/减计数器的步进量为零。

评论