基于FPGA的超声波气体流量计中AGC的实现

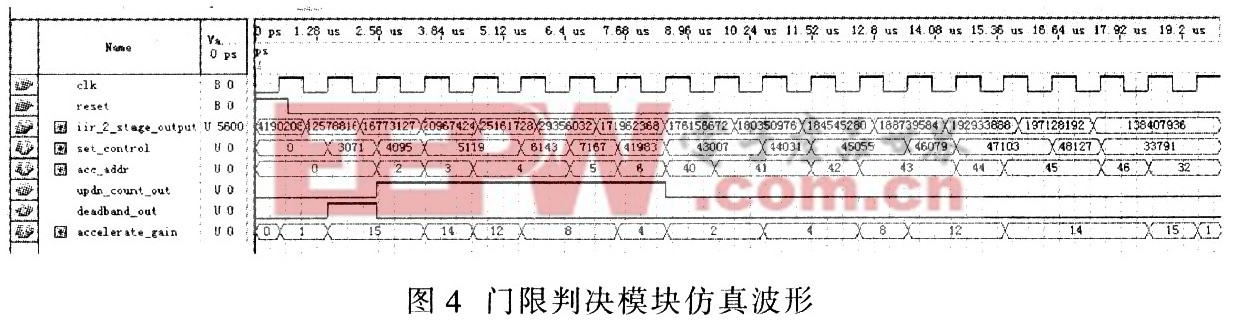

图4是门限判决模块的仿真波形。其中,clk为时钟信号,reset为复位信号,iir_2_stage_output为滤波器的输出信号,set_control为与门限进行比较的信号,acc_addr为查找表地址,updn_count_out为控制加/减计数器的计数方向,dead_band_out为控制加/减计数器的计数控制信号,accelerate_gain为控制加/减计数器的计数步进量。本文引用地址://m.amcfsurvey.com/article/191773.htm

从图4中可以看出,当信号小于低门限7500时,dead_band_out=‘0’,updn_count_out=‘1’,控制加/减计数器向上计数,set_control远离低门限,计数步进量增大;当信号大于高门限10 500时,deadband_out=‘0’,updn_count_out=‘0’,控制加/减计数器向下计数,set_control远离高门限,计数步进量增大。

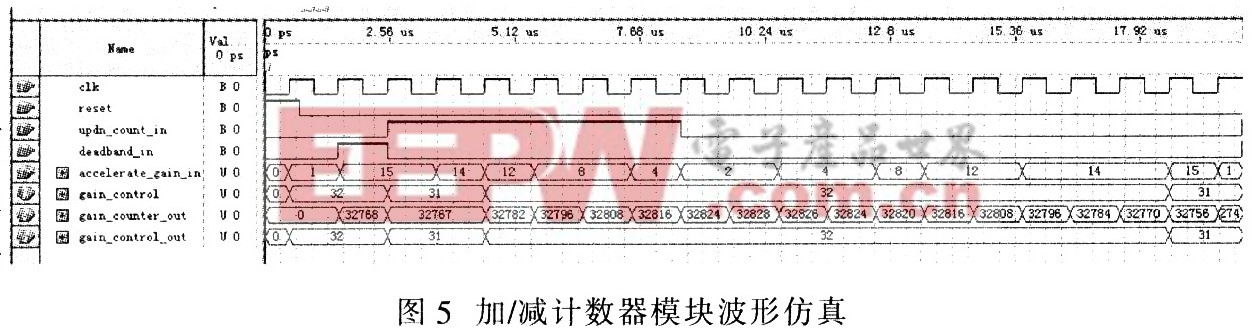

3.2.2 加/减计数器模块

加/减计数器模块根据输入信号与最佳的接收信号之间的差值,对输入信号进行反向补偿。假设输入信号经过一定衰减,AGC环路经过比较可确定接收信号电平低于最佳电平。这个差值将导致计数器向上计数,增加环路增益,直到环路滤波器的输出重新回到门限判决模块的两个门限之间。如果信号乘以增益后、环路滤波器的输出信号大于门限判决模块的高门限时,计数器向下计数,降低环路增益,直到信号重新回到可以准确解调所需的接收信号范围。

图5是加/减计数器模块的仿真波形。gain_counter_out为截位前的增益值,gain_control_out为截位后实际输出的增益值。从图5看出,当reset=‘1’时,计数器复位,设增益初始值gain_control_out=‘32’。而当deadband_in=‘O’,updn_count_in=‘1’,加/减计数器按步进量accelerate_gain_in向上计数;而当deadband_in=‘O’,updn_count_in=‘0’,加/减计数器按步进量accelerate_gainjn向下计数。计数所得的值即为输出的增益控制因子。

4 结论

本文实现了一种全数字AGC的设计方案。此方案可实现40 dB动态范围的控制,并且具有控制精度高,调节速度快,调试简单,受环境影响小,稳定性和可靠性高等优点。随着集成器件的发展,有望实现高动态范围的全数字AGC,以便应用到更广阔的领域中。

评论