用于带有PCIe的嵌入式系统的散/聚式DMA

在PCIe中,通过分割处理来支持读操作,当读请求发出时,PCIe链路上将要传输的数据不会立即得到。在这种情况下,支持延迟处理的DMA控制器将自动放弃总线控制,并允许DMA中任何其他被激活的通道来竞用总线控制。

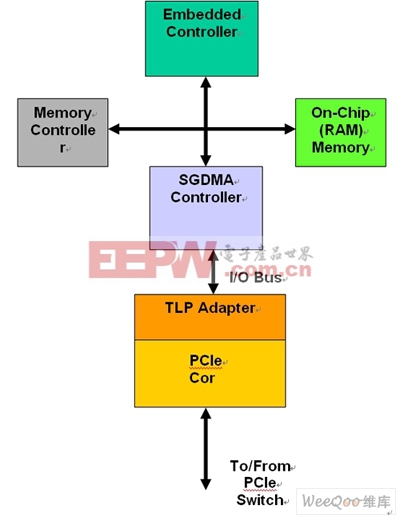

图2:具有DMA高层架构的PCIe。

实时处理方面获得的好处

PCIe串行协议的一些最苛刻的应用是那些要求实时或准实时的数据传递。在这类系统中,像语音和视频处理,需要采用运算增强引擎来满足数据块严格的处理时间要求。这些硬限制不仅增加了运算增强芯片内部的软件工作的数据处理和减小延迟的负担,而且也增加了流处理硬件的负担。一种提供较小的数据包延迟和较高的系统吞吐率的方法是在数据进入系统背板上传输之前,将数据块分成较小的数据包。这样,可以采用较小的接收缓冲器,并确保不会出现哪个数据引擎的负荷过重的问题。

评论