基于PLD的纳秒级脉冲发生器

本设计选用的外部计数时钟频率为100 MHz,因此所产生脉冲的周期最小是10 ns,脉宽调节最小为5 ns,调节步长为5 ns。该脉冲发生器可以实现多路输出,脉冲输出共有9路,其中1路可以实现单脉冲输出,其余8路可以输出不同脉宽的纳秒级脉冲。若要提高脉冲发生器的精度,应提高计数时钟的频率。同时选用速度等级更高的PLD。若要增加脉冲周期及脉宽的可调范围,则应选用容量更大的PLD。

本文引用地址://m.amcfsurvey.com/article/192124.htm2 仿真验证

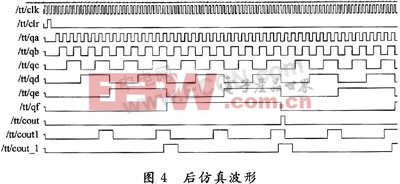

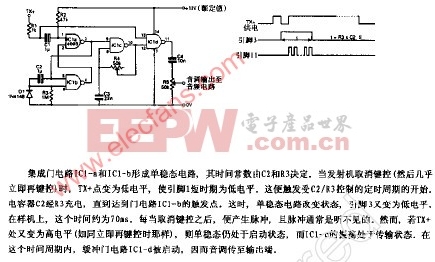

仿真是验证设计的一个重要环节,如果仿真没有通过,设计就必须重来,以便硬件调试的胜利通过。在ISE中,建立仿真文件并调用ModelSim 6.0对设计进行行为仿真。在第2个脉冲到来时进行计数器置零,开始计数,对每个输出端口的波形都进行仿真测试。从仿真波形中可以预测出,可编程器件成功地对脉冲进行控制,然后分频输出,达到预定的要求。

行为仿真只是对VHDL语言进行逻辑综合后仿真,布局布线后仿真则是在具体器件和硬件资源分配后,利用从布局布线中提取的一些信息,其中包括了目标器件及互连线的时延、电阻、电容等信息,并考虑走线之间的相互影响后产生的仿真波形。图4是布局布线后仿真图,可以看到在CLR信号有效开始,输出端经过4个周期的延迟后才响应到有效的复位信号,这个说明器件延时加上互连线延时为4个周期,但是这并不影响设计输出脉冲的质量,在其他电子设计中却要考虑到这个延迟。

|

3 试验结果

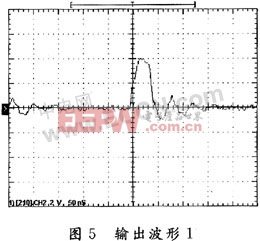

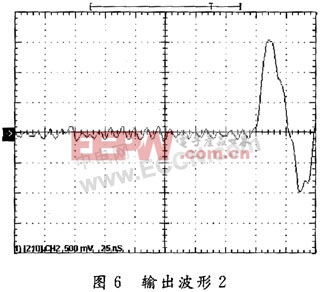

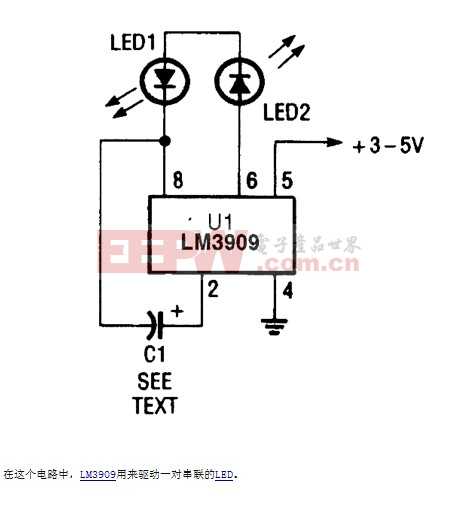

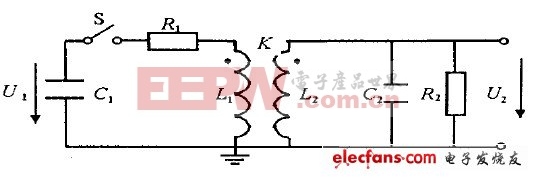

做好电路版,调试程序成功后,用型号为TektronixTDS210示波器测出两个端口的输出波形如图5和图6所示。图5中波形幅度为3.98 V,峰峰值为4.98 V,脉冲宽度为37.8 ns,上升沿为16.7 ns;图6波形幅度为1.53 V,峰峰值为2.51 V,脉冲宽度为19.8 ns,上升沿为9.7 ns。在示波器中显示,得到纳秒脉冲信号非常稳定,可以作为一个稳定的纳秒信号源。每个脉冲过后都有一个小的负脉冲,并且上升沿和下降沿并没有像仿真时短,主要原因是:一是仿真在一个相对理想的条件下进行的,对器件资源在电路中的实际体积忽略;二是芯片的微加工制造工艺不精确,寄生电容电阻的大小没有精确计算,可以在输出端加电容接地减小过脉冲。

|

|

相关推荐

技术专区 |

评论