基于PLD的纳秒级脉冲发生器

4 结 语

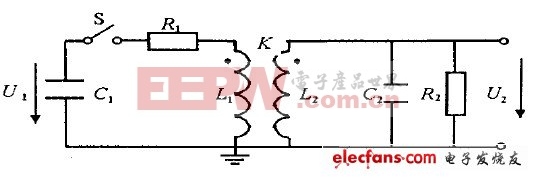

本文引用地址://m.amcfsurvey.com/article/192124.htm本文利用XILINX公司的复杂可编程逻辑器件,结合VHDL语言,提出了一种可控纳秒级脉冲信号发生器的设计方法,并且通过仿真验证,得到脉冲宽度最小为19.8 ns,上升沿为9.7 ns的脉冲。在千伏高压纳秒脉冲发生系统中,采用MOS管、二极管、脉冲形成线等作为核心器件,该信号源必不可少的要一个触发源。利用可控高速信号发生器作为触发源,可以有效地实现对千伏高压的精确控制。在高速数字系统中,数据在器件间的串行传输速率可以达到几百Mb/s。此时,由于时钟周期非常小(通常只有几纳秒),为了保证高速数据的可靠接收,数据与时钟的相对位置要求非常严格,以避免发生数据的错位或在数据变化边沿对数据采样,亦可采用该多路高速信号发生器。简便可靠的纳秒信号发生器在电子系统设计中将越来越具有使用价值。

评论