基于AD7762和FPGA的数据采集系统设计

控制寄存器1的地址是0X0001,设计中控制寄存器1的内容设为0X001B。设计中通过写控制寄存器1设置输出数据频率。读时序控制A/D采样数据的输出。A/D的控制时序及工作状态如图4所示。本文引用地址://m.amcfsurvey.com/article/193417.htm

为低电平期问依次将两个寄存器的地址和内容写入A/D中,控制A/D的工作状态。

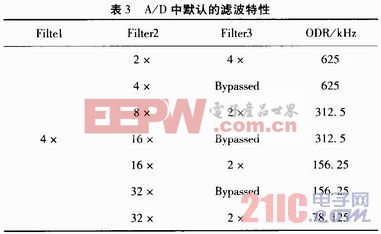

AD7762串联了3个滤波器。通过使用不同的滤波频率、滤波器选择和全通的结合,可以获得大范围的采样速率。通过设置寄存器1的低3位滤波器的状态设置数据输出速率Rate,A/D中默认的滤波特性如表3所示。

表3是在A/D内部时钟为20 MHz时,可看出当rate=3’h3时→625 kHz;rate=3→312.5 kHz;rate=4→156.25 kHz;rate=5→78.125 kHz。

3.2 A/D读时序控制

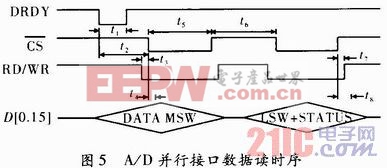

AD7762的读时序如图5所示。

A/D寄存器写成功后,A/D会根据寄存器设置的工作状态进行数据采样和传输。当一个新的转换数据结果有效时,A/D的![]() 引脚会产生一个低脉冲信号送给FPGA,当FPGA接收到这个低脉冲信号时开始接收A/D的采样数据。由于AD7762是24位分辨率的A/D转换器,而外部是16位数据线,所以从AD7762中读取一个转换结果,需要执行两次16 bit读数据操作。当

引脚会产生一个低脉冲信号送给FPGA,当FPGA接收到这个低脉冲信号时开始接收A/D的采样数据。由于AD7762是24位分辨率的A/D转换器,而外部是16位数据线,所以从AD7762中读取一个转换结果,需要执行两次16 bit读数据操作。当![]() 同时为低电平时,数据总线开始传播数据。在二次读操作之间,

同时为低电平时,数据总线开始传播数据。在二次读操作之间,![]() 必须置高一个ICLK周期的高电平。数据传输结束后

必须置高一个ICLK周期的高电平。数据传输结束后![]() 保持高电平,数据线处于高阻态,等待下一次有效数据的传输。

保持高电平,数据线处于高阻态,等待下一次有效数据的传输。

评论