基于DM642的实时多协议转换器设计

2 硬件设计

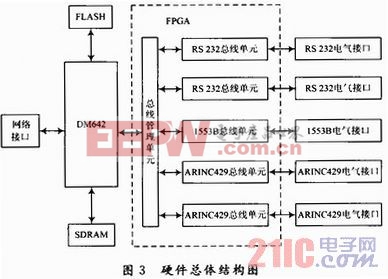

本系统采用如图3所示的DM642+FPGA的设计方式,实现了双通道RS 232总线、双通道ARINC429,单通道双冗余1553B总线以及LAN总线的通信。DM642为TI公司的C6000系列高速DSP,其主频最高可达720 MHz,数据处理能力达4 800 MIPS,其收发通道独立的EMAC和MDIO可以很好的支持10 Mb/s和100 Mb/s以太网。DM642还扩展32 MB SDRAM和8 MB FLASH,用于缓存数据和存储协议。FPGA选择Altera公司的EP3C55F4 84,其LE单元、储存单元、可用I/O均比较丰富。DM642实现以太网接口,控制系统并完成协议的编解码。FPGA中的总线单元实现RS 232等总线的物理层收发,总线管理单元协调DM642与各总线单元间的通信。采用专业芯片实现各总线的电气转换。本文引用地址://m.amcfsurvey.com/article/194140.htm

总线管理单元管理各总线,并协调各总线与DM642的通信。为防止总线冲突,总线管理单元中记录DM642及RS 232等总线单元的工作状态。1553B总线与RS 232总线和ARINC429总线不同,其收发是相关的,无论其收发数据时,总线管理单元都视其被占用。当DM642处理高优先级协议时,总线管理单元将对DM642屏蔽低优先级协议产生的中断,直至DM642完成相应数据处理。对为了防止总线被“锁死”,总线管理单元对超过一定时长处于忙状态而未被使用的总线复位,并对DM642产生总线异常中断。

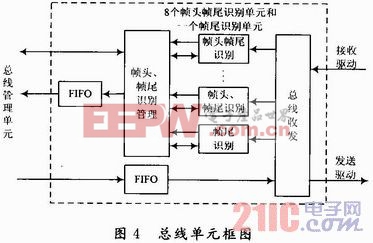

每个总线单元都采用如图4所示的结构,“总线收发”实现相应总线物理层收发。在总线单元中实现8个帧头识别单元和一个帧尾识别单元,实时匹配和提取协议。帧头识别单元记录有高优先级协议的帧头、帧尾、帧长等信息,DM642在识别出低优先级协议后,将该协议的帧尾、帧长等信息写入帧尾识别单元。无论是DM642还是任一帧头帧尾识别单元协议匹配成功后,帧头帧尾识别管理单元都将使其它帧头帧尾识别单元处于非工作状态,在该帧头帧尾识别单元根据帧尾或帧长提取完协议后,其它帧头帧尾识别单元将再次使能。帧头帧尾识别管理单元在识别出协议和完成协议提取时,将向总线管理单元产生不同中断。总线发送FIFO由非空变为空,也产生发送完成中断。

评论