基于DM642的实时多协议转换器设计

3 软件设计

3.1 协议存储、加载方法

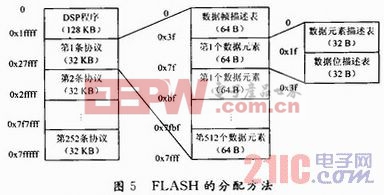

为了使上电复位后无需重新加载协议,将协议描述表存储于FLASH中,FLASH的分配方法的存储空间分配方法如图5所示。本文引用地址://m.amcfsurvey.com/article/194140.htm

8 MB存储空间的前128 KB存储空间用于存储DSP程序,剩余的空间划分为252个32 KB大小的数据块,每个数据块用于存储一条协议的所有信息;每个32 KB大小数据块在划分为512个64 B大小的次级数据块,第1个次级数据块用于存储数据帧描述表,后511个次级数据块存储数据元素的相关信息;64 B存储空间的前32 B用于存储数据元素描述表,后32 B用于存储数据位描述表,同一个数据元素最多支持8个数据位操作。采用这种协议存储方法的好处是,方便了协议的加载及修改,DM642很容易计算出每个数据帧、数据元素、数据位描述表的地址,加快了协议信息的查找,但对存储空间的浪费也比较大。

3.2 DSP程序设计

软件程序调用CCS 2提供实时操作系统DSP/BIOS,DSP/BIOS采用抢先式多任务内核,支持硬件中断、软件中断、任务、后台线程等4种线程,并提了同步机制。在DSP/BIOS下调用NDK的函数库进行TCP/IP协议编程时,需配置EMAC并开启线程监控网络接口,参考文献详细介绍了DSP/BIOS下的TCP/IP协议编程,这里把网络总线视为普通接口。

为了保证系统实时性,需合理使用DSP/BIOS提供的不同类型线程,并协调好各线程间的通信。协议及各总线的配置数据均存储于FLAS-H,也上电后通过以太网在线动态加载至DM642。在主线程中对DM642和FPGA进行初始化配置。硬件中断的实时性最高,监控各总线状态,并根据从FPGA读回的中断信息,生成相应消息并触发软件中断和线程。硬件中断的流程如图6所示,依次扫描各总线中断信息,根据中断信息触发总线异常、接收数据、帧头识别、协议接收完成、发送完成等中断的处理程序。

评论