基于Linux平台的天气雷达高速数据采集系统设计

Linux是开放源代码、网络化的操作系统,具有稳定、高效、内核可自由配置等特点。采用Linux操作系统作为开发平台与采用VxWorks 和Windows 作为开发平台相比不仅有免费的优势,而且对于发展核心技术,提高信息安全有着极其重要的意义,是自主研发的一个方向。随着我国天气雷达的快速发展,天气雷达在民用和军事领域的应用越来越广泛。目前,天气雷达高速数据采集、传输等功能大都基于Windows平台进行开发实现,实现由Windows平台向Linux平台的转换,对于发展中国自主知识产权气象软件核心技术, 提高信息安全有着极其重要的意义。本文基于Linux 操作系统(2.6.23内核),实现了天气雷达高速数据采集及处理,对天气雷达系统由Windows平台向Linux平台移植具有参考价值。

本文引用地址://m.amcfsurvey.com/article/194993.htm1 数据采集系统分析

1.1 工作原理

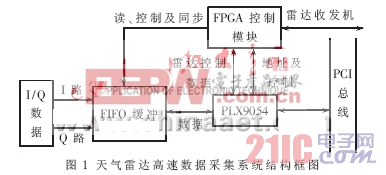

天气雷达高速数据采集系统由I/Q数据采集、FIFO缓冲、FPGA控制模块及PCI总线芯片PLX9054组成,系统结构框图如图1所示。

其核心部分为FPGA控制模块,主要实现4个功能:(1)根据雷达量程和距离分辨率调整AD采样时钟的频率;(2)控制AD两路采样数据写入FIFO 缓冲以及DMA 传输时从FIFO中连续读出数据; (3)与PCI总线控制芯片PLX9054 进行控制交互, 实现局部总线的读写控制、地址译码和中断触发;(4)与PLX9054 进行数据交互,使用FPGA内部RAM保存控制天气雷达发射机和接收机工作的命令及数据,完成对雷达工作的控制。

I/Q数据采集输出数据速度为2.4 Mb/s(I、Q数据各为24 bit),通过FPGA控制,合并写入到FIFO缓冲。FIFO缓冲为32 bit、深度为16 KB的数据缓存,有效位为24 bit;与计算机总线的接口采用32 bit的PCI总线接口芯片PLX9054,PC机通过它完成与数据采集系统的数据交互。

1.2 PC机与采集系统数据访问

1.2.1 局部地址分配

PC机与天气雷达高速数据采集系统的数据访问通过PCI总线芯片PLX9054实现,访问目标为FIFO缓冲和FPGA片内RAM。对FIFO缓冲和FPGA片内RAM分配不同局部地址,通过对局部地址总线进行译码确定需要访问的目标。FIFO 数据采用DMA传输方式连续读出, 每次传输长度最大为8 KB,因此,设置FIFO空间32 bit局部地址范围为0x20000000~0x2000FFFF,映射空间为PCI 地址空间bar2。

FPGA片内RAM位宽为32 bit, 采用局部地址范围为0x40000000~0x400FFFFF。映射空间为PCI地址空间bar3。

linux操作系统文章专题:linux操作系统详解(linux不再难懂)

评论