基于FPGA+DSP的雷达回波发生器设计

采用DSP和FPGA/CPLD相结合的系统结构综合了两者在系统控制和实时数字信号处理方面的优势,结构灵活、实现性强[1]。本文提出了一种以FPGA为核心,DSP实时控制,外加PROM、Flash、CPLD以及D/A等外围电路构成的雷达中频回波信号发生器的设计方法,可以通过在线编程在相同的硬件平台上实现不同体制、多目标的雷达回波。

1 雷达回波发生器方案设计

1.1 系统性能要求

本雷达回波发生器是为了对雷达信号处理机进行测试、评估以及新的信号处理算法而开发研制的,因而在设计上要满足通用性要求,能模拟产生不同体制雷达的回波信号[2]。通用性设计要求硬件外围接口电路尽可能简单,对各种电平规范具有兼容性;所选器件适应性强,通过重配置可编程逻辑电路即可产生不同带宽、不同时宽的雷达信号而不用修改硬件设计[3-4]。同时,为了真实地反映雷达目标的复杂环境,要求雷达回波发生器能加入噪声和干扰,从而能够对信号处理机进行全面的评估和检测。

本雷达回波发生器要求能选择产生单脉冲跟踪、DBF、SAR 3种体制雷达的最多3个目标的回波信号,雷达波形为简单脉冲、线性调频信号、相位编码信号可选。主要技术指标如下:

(1)中频载频频率:30 MHz;

(2)系统基准时钟:10 MHz;

(3)波形存储深度为10 K,信号采样率100 MHz;

(4)幅度分辨率为12 bit;

(5)频率范围为0.37 Hz~25 MHz,频率分辨率为0.37 Hz;

(6)输出模拟信号幅度范围为±2.5 V;

(7)DBF体制时天线阵元数为16个。

1.2 系统实现方案

雷达回波发生器的实现有以下3种方法:全硬件实现、微机+D/A插卡实现以及微机+模拟器DSP组合实现。由于全硬件实现时硬件设计过于复杂、灵活性差、微机+D/A插卡方法受D/A数据传输率的限制,所以目前雷达回波发生器的设计中,多采用微机+模拟器DSP组合方法。该方法灵活性好、数据量适中、易扩充、满足通用性要求[5]。

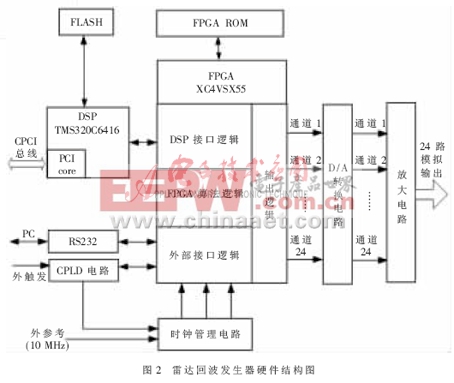

通过对几种回波发生器实现方法的比较,结合本雷达回波发生器要实现的功能以及灵活性、通用性的设计思想,本文提出了一种新的雷达中频回波发生器的设计与实现方法。该方法严格说仍属于微机+模拟器DSP组合方法,但采用了微机+FPGA+DSP+D/A的组合,如图1所示。

与传统的雷达回波发生器实现方法相比,采用该结构具有以下优点:

(1)PC机不必实时为回波发生器提供数据,只是在雷达参数改变时,PC机才给存储器输入新的波形和参数数据。这样便能采用更为逼真的雷达回波数学模型,并能对这些模型完成更为复杂和精确的处理工作,提高模拟信号环境的逼真性;

(2)硬件实现简单,只要改变底层软件而不用更改硬件电路就可以适应不同体制的雷达,因而这种方法具有较好的灵活性和通用性;

(3)对外具有丰富的接口,既可以当作一块独立的板卡使用,也可以在CPCI机箱上作为标准板卡使用;

(4)利用其丰富的底层软件库,可以提供良好的二次开发空间。

2 系统硬件设计

雷达回波发生器在硬件实现时,FPGA选用Xilinx公司Virtex-4系列的XC4VSX55芯片, DSP选用TI公司的TMS320C6416芯片,数模转换器和放大器分别选用ADI公司的AD9765和AD8044,时钟选用ADI公司的超低抖动时钟ICAD9510,时钟配置电路选用Altera公司MAX7000S/AE系列的EPM7128S。SX55是Xilinx公司的一款高性能数字信号处理FPGA,具有强大的数据处理能力。主要硬件资源为49 152个SLICE(含一个触发器及一个四输入查找表),320个BLOCK RAM(每块18 KB),512个18×18 bit乘法器,8个DCM,32条全局时钟连线,640个可用I/O。TMS320C6416是TI公司的一款高性能定点数字信号处理器,最高工作时钟600 MHz,可达4 800 MIPS。主要硬件资源有128 KB L1P cache,128 KB L1D cache,8 MB L2 cache。两个外部存储器接口(EMIF),EMIFA为64 bit,EMIFB为16 bit,共1 280 MB外部地址。64个EDMA,32 bit或16 bit HPI接口,PIC接口。雷达回波发生器的硬件结构如图2所示。

系统的工作流程是:

(1)雷达波形数据的计算产生。通用计算机根据输入的雷达参数计算得到雷达基带信号波形数据,以备通过RS-232串行接口传输给大容量波形存储器存储。

(2)数据传输。FPGA通过电平转换芯片与串口相连,将经RS-232串行接口送来的通用计算机产生的雷达基带信号数据以及雷达目标、噪声有关参数接收并存储在其内部设计的存储器中。

(3)实时信号处理。FPGA对存储数据进行延时、多普勒调制、幅度控制、中频调制以及噪声加载等信号处理,得到雷达回波的数字信号。当雷达参数或目标属性、噪声参数改变时,DSP更新存储器中存储的数据。

评论