通用线阵CCD采集系统设计

2.2 通用驱动采集板

通用驱动采集板由A/D转换、FPGA(通用CCD驱动器模块和16In8Out异步FIFO模块)、USB 3部分组成。A/D转换部分完成系统的A/D转换;FPGA部分完成系统的CCD驱动、数据采集、CDS实现;USB部分完成数据的传输。

2.2.1 A/D转换部分

系统需采集多种CCD并实现CDS,而且系统主要由USB供电,这就要求A/D转换速度快,供电电压低,最好参考电压内置。AD9235-40属于12位、40 MS/s模数转换器系列,采用3 V单电源供电,该系列均内置一个高性能采样保持放大器(SHA)和基准电压源。AD923540采用多级差分流水线架构,内置输出纠错逻辑,在40 MSP/S数据速率时可提供12位精度,并保证在整个工作温度范围内无失码。

FPGA中采集信号发生器提供A/D采集时钟,同时也控制FIFO和CCD驱动器。A/D采样速率不再受数据传输和采集制约,采样速率完全和CCD速度匹配。并可实现1帧内1个像元的双采样,从而实现CDS。

2.2.2 FPGA部分的通用CCD驱动器模块

由于不同生产商的CCD器件的驱动时序往往差别很大,因此需针对每种CCD器件编制其CCD驱动器模块。驱动时钟和采集脉冲由分频器和采集信号发生器提供,如图2所示。

CCD驱动器输入信号由两路驱动时钟和积分时间控制信号INT组成;输出信号由帧同步信号FS和CCD Driver信号组成。不同的CCD驱动器模块仅CCD Driver信号有所不同,其他接口一样。在改变CCD时只需替换CCD驱动器模块即可。

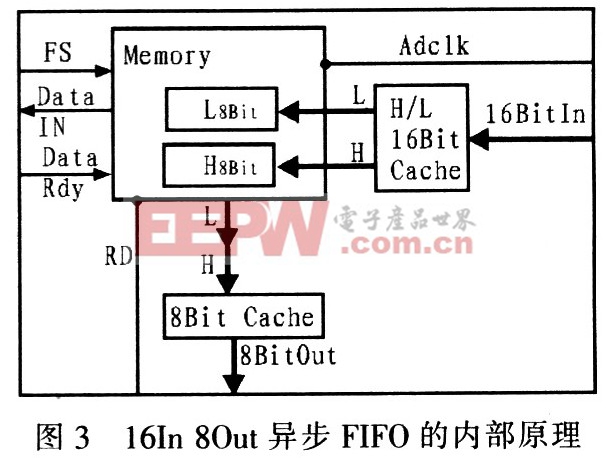

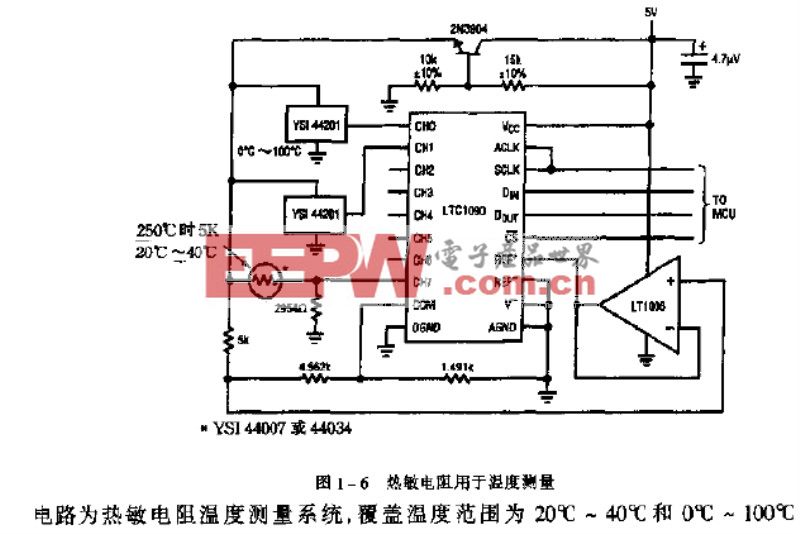

2.2. 3 FPGA部分的16In8Out异步FIFO

FIFO用于暂存A/D转换的信号。待存满1帧并且USB块传输空闲后,将FIFO中的1帧数据通过快速块传输上传至计算机。1帧的像元个数由CCD驱动模块提供的FS信号决定。FIFO内的存储空间为192 Kb。满足线阵CCD和小型面阵CCD的数据存储需求。图3为16In8Out异步FIFO的内部原理图。

评论