通用线阵CCD采集系统设计

图3中,FS是帧同步,在FIFO中重置暂存指针,DataIN是暂存数据采集完毕信号,DataRdy是判断USB是否空闲信号,ADclk是FIFO的写信号,16BitIN是FIFO的读16位入口,读取A/D信号,这里兼容16位,本设计只用12位,其他4位空闲。8BitOUT是FIFO的8位输出口,RD是FIFO的读出时钟信号。在FIFO中读入的16位信号分高低位分别存储在2个8 bit存储器中,在输出时,按先高后低的顺序输出,从而完成16In8Out的转换,部分实现代码如下:

在信号FS的控制下,FIFO不断地对整帧信号进行刷新,当USB传输信号到来时,刷新当前帧完毕后,开始USB快速读入操作。

2.2.4 USB部分

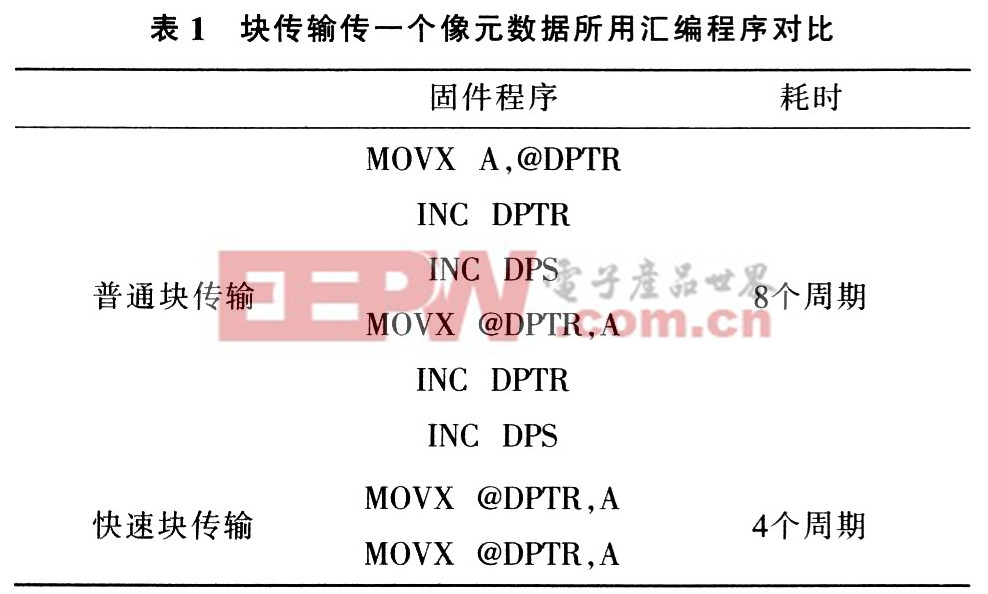

USB采用Cypress公司的AD2131Q,其核提供一种快速传输模式.改进8051的外部逻辑与同步/块端点缓冲器之间的传输速度。将FASTXFR寄存器设置为01010000B,读写选通时序模式为10,提供更宽的脉冲宽度,便于读取FPGA的异步FIFO信号。FIFO存储满1帧数据,由USB器件使用快速块传输上传到计算机,约6 ms完成。表1为块传输传一个像元数据所用汇编程序对比。

评论