STM32 NVIC 中断优先级管理

在MDK内,与NVIC相关的寄存器,MDK为其定义了如下的结构体:

本文引用地址://m.amcfsurvey.com/article/201611/317044.htm- typedefstruct

- {

- vu32 ISER[2];

- u32 RESERVED0[30];

- vu32 ICER[2];

- u32 RSERVED1[30];

- vu32 ISPR[2];

- u32 RESERVED2[30];

- vu32 ICPR[2];

- u32 RESERVED3[30];

- vu32 IABR[2];

- u32 RESERVED4[62];

- vu32 IPR[15];

- }NVIC_TypeDef;

STM32的中断在这些寄存器的控制下有序的执行的。只有了解这些中断寄存器,才能了解STM32的中断。下面简要介绍这几个寄存器:

ISER[2]:ISER全称是:InterruptSet-EnableRegisters,这是一个中断使能寄存器组。上面说了STM32F103的可屏蔽中断只有60个,这里用了2个32位的寄存器,总共可以表示64个中断。而STM32F103只用了其中的前60位。ISER[0]的bit0~bit31分别对应中断0~31。ISER[1]的bit0~27对应中断32~59;这样总共60个中断就分别对应上了。你要使能某个中断,必须设置相应的ISER位为1,使该中断被使能(这里仅仅是使能,还要配合中断分组、屏蔽、IO口映射等设置才算是一个完整的中断设置)。具体每一位对应哪个中断,请参考stm32f10x_nvic..h里面的第36行处。

ICER[2]:全称是:InterruptClear-EnableRegisters,是一个中断除能寄存器组。该寄存器组与ISER的作用恰好相反,是用来清除某个中断的使能的。其对应位的功能,也和ICER一样。这里要专门设置一个ICER来清除中断位,而不是向ISER写0来清除,是因为NVIC的这些寄存器都是写1有效的,写0是无效的。

ISPR[2]:全称是:InterruptSet-PendingRegisters,是一个中断挂起控制寄存器组。每个位对应的中断和ISER是一样的。通过置1,可以将正在进行的中断挂起,而执行同级或更高级别的中断。写0是无效的。

ICPR[2]:全称是:InterruptClear-PendingRegisters,是一个中断解挂控制寄存器组。其作用与ISPR相反,对应位也和ISER是一样的。通过设置1,可以将挂起的中断接挂。写0无效。

IABR[2]:全称是:InterruptActiveBitRegisters,是一个中断激活标志位寄存器组。这是一个只读寄存器,通过它可以知道当前在执行的中断是哪一个。在中断执行完了由硬件自动清零。对应位所代表的中断和ISER一样,如果为1,则表示该位所对应的中断正在被执行。

IPR[15]:全称是:InterruptPriorityRegisters,是一个中断优先级控制的寄存器组。这个寄存器组相当重要!STM32的中断分组与这个寄存器组密切相关。因为STM32的中断多达60多个,所以STM32采用中断分组的办法来确定中断的优先级。IPR寄存器组由15个32bit的寄存器组成,每个可屏蔽中断占用8bit,这样总共可以表示15*4=60个可屏蔽中断。刚好和STM32的可屏蔽中断数相等。IPR[0]的[31~24],[23~16],[15~8],[7~0]分别对应中断3~0,依次类推,总共对应60个外部中断。而每个可屏蔽中断占用的8bit并没有全部使用,而是只用了高4位。这4位,又分为抢占优先级和子优先级。抢占优先级在前,子优先级在后。而这两个优先级各占几个位又要根据SCB->AIRCR中的中断断分组设置来决定。

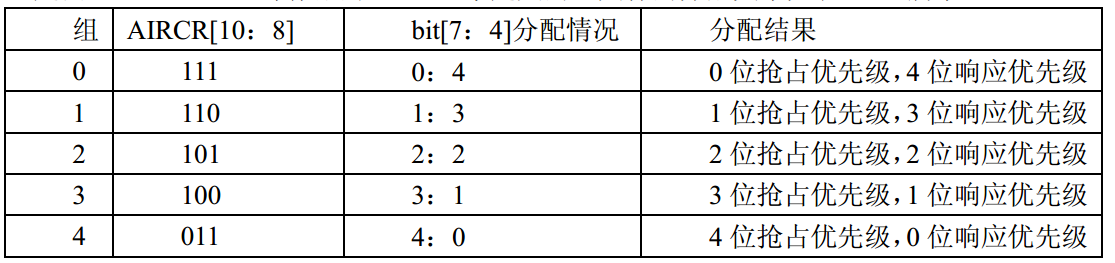

这里简单介绍一下STM32的中断分组:STM32将中断分为5个组,组0~4。该分组的设置是由SCB->AIRCR寄存器的bit10~8来定义的。具体的分配关系如表

通过这个表,我们就可以清楚的看到组0~4对应的配置关系,例如组设置为3,那么此时所有的60个中断,每个中断的中断优先寄存器的高四位中的最高3位是抢占优先级,低1位是响应优先级。每个中断,你可以设置抢占优先级为0~7,响应优先级为1或0。抢占优先级的级别高于响应优先级。而数值越小所代表的优先级就越高。

这里需要注意两点:第一,如果两个中断的抢占优先级和响应优先级都是一样的话,则看哪个中断先发生就先执行;第二,高优先级的抢占优先级是可以打断正在进行的低抢占优先级中断的。而抢占优先级相同的中断,高优先级的响应优先级不可以打断低响应优先级的中断。

使用库函数实现以上中断分组设置以及中断优先级管理,使得我们以后的中断设置简单化。NVIC中断管理函数主要在misc.c文件里面。

首先是中断优先级分组函数NVIC_PriorityGroupConfig,这个函数的作用是对中断的优先级进行分组,这个函数在系统中只能被调用一次,一旦分组确定就最好不要更改。

比如我们设置整个系统的中断优先级分组值为2(2位抢占优先级,2位响应优先级”),那么方法是:NVIC_PriorityGroupConfig(NVIC_PriorityGroup_2);

设置好了系统中断分组,那么对于每个中断又怎么确定他的抢占优先级和响应优先级呢?下面看一个重要的函数为中断初始化函数NVIC_Init,其函数申明为:

voidNVIC_Init(NVIC_InitTypeDef*NVIC_InitStruct)

其中NVIC_InitTypeDef是一个结构体,可以看看结构体的成员变量:

- typedefstruct

- {

- uint8_t NVIC_IRQChannel;//定义初始化的是哪个中断,这个我们可以在 stm32f10x.h 中找到每个中断对应的名字。例如 USART1_IRQn。

- uint8_t NVIC_IRQChannelPreemptionPriority;//定义这个中断的抢占优先级别。

- uint8_t NVIC_IRQChannelSubPriority;//定义这个中断的子优先级别。

- FunctionalState NVIC_IRQChannelCmd;//该中断是否使能。

- }NVIC_InitTypeDef;

比如我们要使能串口1的中断,同时设置抢占优先级为1,子优先级位2,初始化的方法是:

- USART_InitTypeDef USART_InitStructure;

- NVIC_InitStructure.NVIC_IRQChannel=USART1_IRQn;//串口 1 中断

- NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority=1;// 抢占优先级为 1

- NVIC_InitStructure.NVIC_IRQChannelSubPriority=2;// 子优先级位 2

- NVIC_InitStructure.NVIC_IRQChannelCmd=ENABLE;//IRQ 通道使能

- NVIC_Init(&NVIC_InitStructure);

评论