S3C44B0X应用设计 - 存储器组设计

S3C44B0X 有6组ROM/SRAM(ROM0 组为Boot ROM)和2组ROM/SRAM/FP/EDO/SDRAM.S3C44B0X 中的系统管理能够通过S/W 控制每组的访问时间、数据总线宽度,ROM/SRAM 组的访问时间和 FP / EDO / SDRAM 组被系统管理寄存器中的BANKCON0-7和BANKCON6-7控制。组6-7的类型需要相同。(例如ROM&ROM,SDRAM&SDRAM)每组ROM/SRAM/DRAM的数据宽度受BWSCON 控制寄存器控制。

ROM 组0用于Boot ROM 组,因此组0受H/W控制,OM[1:0]用于这个目的的。

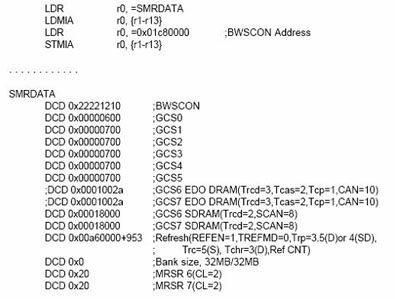

当系统复位时,通过专用的命令,LDMIA和STMIA 对 BWSCON,BANKCON0-7,BANKSIZE, MRSRB6/7实施控制。例如下面代码用来配置特殊功能寄存器。特殊功能寄存器配置代码:

ROM/SRAM组的设计

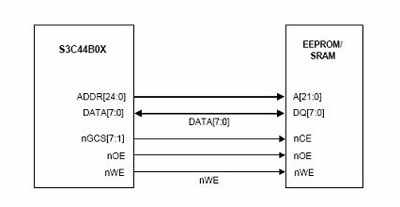

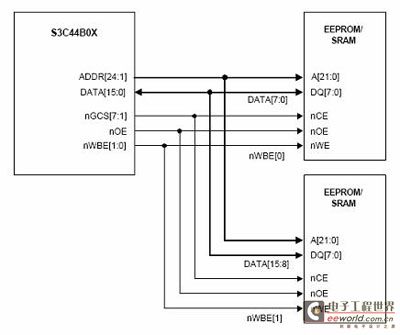

ROM/SRAM 组1-7,可以有着不同的数据总线宽度,总线宽度是受 S/W 控制的,一个 ROM/SRAM 组1-7 的设计样例如图 4-6,图 4-7,图 4-8 和图 4-9 所示。

图 4-6.单字节 EEPROM/SRAM Banks 设计

图 4-7.半字 EEPROM/SRAM 组设计

评论