基于8086 CPU的单芯片计算机系统的设计

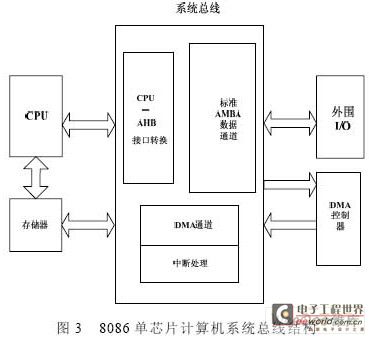

AMBA 拥有众多第三方支持,在基于ARM处理器内核的SoC 设计中,已经成为广泛支持的现有互联标准之一。2.0 版AMBA 标准定义了三组总线:AHB(AMBA 高性能总线)、ASB(AMBA 系统总线)、和APB(AMBA 外设总线)。AHB 的总线架构的相互连接采用了传统的带有主模块和从模块的共享总线模式,接口与互连功能分离,这对芯片上模块之间的互连具有重要意义。因此,本论文所选择的总线遵从AHB 总线传输的基本规范,并在此基础上针对8086CPU 的特点增加和修正了某些总线的接口。整个设计主要包括两方面的内容:AHB 和8086 传输时序的匹配;基于8086CPU 的总线接口的扩展设计。总线结构图如图3 所示。

3.2.2 传输时序的匹配

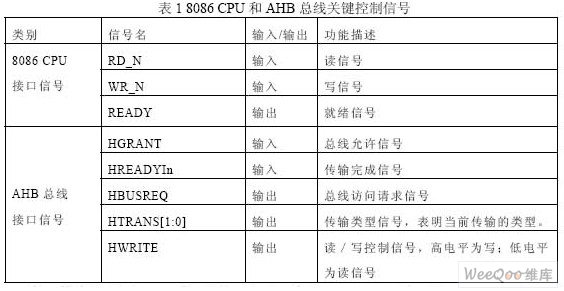

因为AHB 总线和CPU 的传输协议不同,所以需要匹配两个接口的时序,以保证CPU与其他外围IP 可以通过总线正常通信。相关接口控制信号如表1 所示。

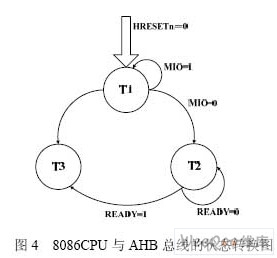

接口模块首先根据MIO 信号判断访问的是存储器还是I/O 设备,如果是I/O 设备,当采样到READY 信号为高电平时,获取AHB 的总线控制权,与外围I/O 设备进行通信。设计的状态机如图4 所示。

T1:根据MIO 信号判断当前CPU 是否需要访问外围I/O。如果8086 处理器核访问的是存储器单元而不是AHB 总线上的设备(即MIO 为1),状态机则保持T1 状态,并且不向AHB 总线发出总线请求信号(即HBUSREQ 信号置为0)。MIO 为低电平则跳转到T2。

T2:状态机进入T2 状态后,向AHB 总线发出总线请求信号(即HBUSREQ 信号置为1),向AHB 总线仲裁器请求访问总线。同时检测READY 信号,当检测到READY 信号为高电平,即AHB 总线仲裁器把总线访问权限交给8086 处理器核,状态机在下个时钟上升沿进入T3 状态。反之,如果READY 一直为低电平,表示目前8086 CPU 要访问的AHB 总线上的从设备没有准备就绪,要求8086 处理器核插入等待状态,状态机一直保持T2 状态不变。

T3:CPU 通过AHB 总线与外围IP 进行通信,直至通信结束,返回到T1 状态。

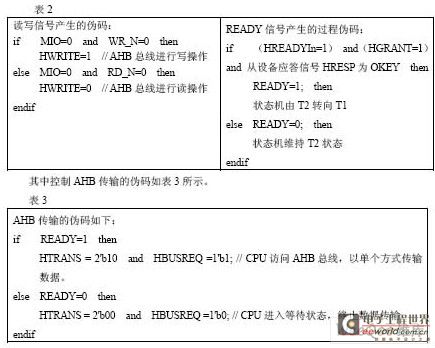

8086 处理器核的读写信号受READY 信号控制,当READY 信号为高电平时,可进行数据的接收和发送,否则读写信号保持。READY 信号由AHB 总线上从设备传输完成信号HREADYIn、AHB 总线允许信号HGRANT 以及从设备应答信号HRESP 三者共同决定。而总线上的读写控制信号HWRITE 由组合逻辑产生。其产生过程伪码如表2 所示。

3.2.3 总线接口扩展

8086CPU 除了数据、地址总线以及读写和READY 等主要控制信号外,还有中断请求和应答以及外接DMA 设备的相关端口信号。而这些信号是标准AHB 总线所不具备的,因此还需要扩展总线接口以匹配8086 CPU。总线接口的扩展设计主要包括两部分:中断处理和DMA 数据通道。8086 CPU 关于中断和DMA 的端口信号如表4 所示。

评论