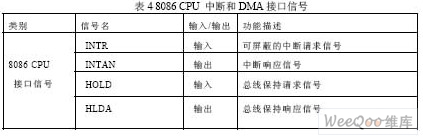

基于8086 CPU的单芯片计算机系统的设计

系统总线在接收到外设的中断请求之后,会向CPU 提出中断申请,一旦接收到中断响应,要向外设传送中断响应信号,同时修改译码单元,选通该外设,保证在第二个中断响应期间能将中断类型号通过总线传送给CPU,使得CPU 能成功跳转到中断服务子程序。

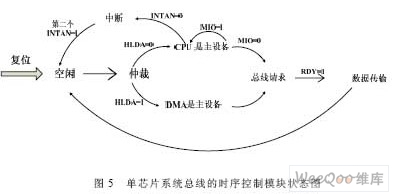

DMA 控制器在执行数据传输时,需要掌握AHB 总线的控制权,向片上存储器或者总线上其他外设发出地址和控制信号,即相当于AMBA 的主设备;另一方面,在DMA 控制器启动工作之前,CPU 需要对其进行预处理操作,以使其按照特定的配置参数进行工作,在这个初始化阶段,CPU 是AHB 总线上的主设备,DMA 控制器属于从设备。基于DMA控制器的这种两面性,在总线设计中配备了专门的DMA 通道与其相匹配:CPU 正常工作时,

DMA 扮演从设备的角色,接受CPU 对其的初始化;利用HLDA 作仲裁信号,当CPU 响应外设DMA 请求时(即HLDA 为高电平),让出总线控制权给外设,利用DMA 数据通道传输数据,传输的协议同样遵从AMBA 协议。总线的时序控制模块状态如图5 所示。

3.3 存储单元的接口设计

存储器子系统包括一个RAM 和一个ROM,8086CPU 支持20 位地址总线,具有1M 字节存储空间,分为RAM 区和ROM 区。本文利用开发板的片上ROM 资源配置成16k*16 的格式作为存储器中的ROM 单元,采用DE2 开发板上的8M 的SDRAM 配置成256K*16 位总线格式代替存储器中的RAM 单元。

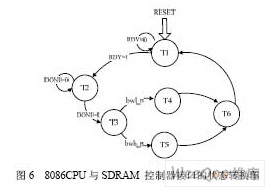

在各种随机存储器件中,SDRAM 的价格低,体积小,速度快,容量大,是比较理想的器件。但SDRAM 的控制逻辑比较复杂,对时序要求也十分严格,这就要求有一个专门的控制器:控制SDRAM 的初始化,刷新和预冲以及基本的读写操作。同时,需要匹配SDRAM控制器和8086 CPU 的读写时序。该接口具体实现的状态机如图6 所示。

T1:当RDY 为高电平时,首先确定是进行读还是写操作,这时DONE 为0:读:设置WR=0,RD=1; 写:设置WR=1,RD=0。

T2:当DONE 信号为高电平,表示可以进行读/写操作,跳转到T3。

T3:CPU 通过SDRAM 控制器对SDRAM 进行读写操作。

T4:当低字节有效信号bwl_n 为高电平时,执行低字节传输。

T5:当高字节有效信号bwh_n 为高电平时,执行高字节传输。

T6:CPU 完成读写操作,相关控制信号清零。

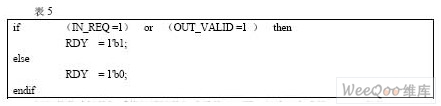

其中,DONE 信号用于指示是否读写完成,只有DONE 为高电平时表示读写完成,才能进行下次读写操作。RDY 信号表示SDRAM 是否做好准备接受CPU 的访问,由SDRAM的写请求信号(IN_REQ =1)和读有效信号(OUT_VALID =1 )共同控制,其产生过程伪码如表5 所示。

根据单芯片计算机系统级设计的组成结构,调用已经编写完成的8086 IP 软核、8255 IP软核、SDRAM 控制器、SDRAM 模型IS42S16400、AHB 总线 IP 软核以及译码器IP 软核。

连接相应的输入输出端口,同时对8086 相关的输入端口进行赋值,将未使用的输出端口悬空,完成单芯片计算机系统的RTL 级设计。

4 单芯片计算机系统的仿真与验证

单芯片计算机的RTL 级设计只是全部设计流程的一部分,为保证最终设计的成功,必须对其进行全面的软件仿真与硬件验证,包括搭建测试平台,设计测试方案以及分析仿真结果,实现FPGA 验证。

4.1 测试方案的设计

在包含8255 应用电路的单芯片计算机系统搭建完成的基础上,要求实现八个开关量控制八个LED灯亮灭的功能。将八个开关量连接8255 的PA0~PA7;将八个LED 灯驱动电路连接8255 的PC0~PC7。在8086 CPU 的控制下,通过总线读取连接在8255 PA 口的八个开关量,将开关值送往SDRAM 存储,再从SDRAM 读取开关量发送到8255 PC 口,使其驱动八个LED 灯的亮或灭。

4.2 仿真结果分析

单芯片计算机最小集的RTL 级仿真波形,如图7 所示。在8086 CPU 的控制下,8255接口读取连接在8255 PA 口的八个开关量11000010 以后,将其发送到8255 的PC 口,驱动输出逻辑值11000010。

使用QuartusII 软件成功编译设计,将布局布线生成的结果下载到FPGA 中,得到与设计等效的实际电路,对实际的电路用测试系统进行测试,从而验证设计的正确性。将FPGA的验证结果经逻辑分析仪读取显示,如图8 所示。

5 结束语

本论文在基于集成电路设计方法学的指导下,探讨了一种基于8086 CPU 核的单芯片计算机平台的架构,研究了其与AMBA 总线、SDRAM、8255 等外围IP 的集成。在此基础上,设计基于8086 IP 软核的单芯片计算机系统,并实现了FPGA 功能演示。在后续的工作中,将考虑进一步扩展CPU 外围接口IP 软核;集成DMA 控制器,实现VGA 显示功能;将DOS 操作系统加入8086 单芯片计算机平台,并开发在操作系统下的设备驱动程序和应用软件。

评论