一种智能ARI NC429总线接口板的硬件设计与实现

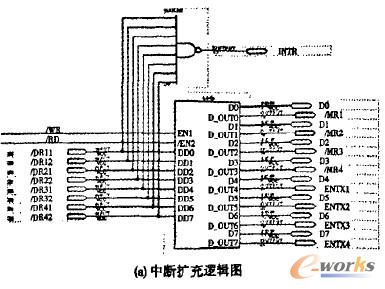

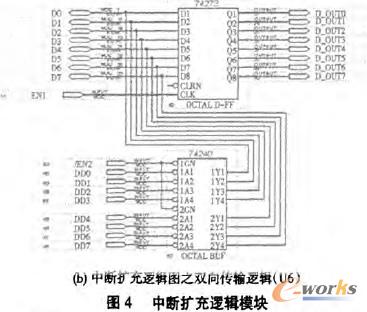

(3)中断扩充逻辑模块。由于F206的IO引脚数量及其有限,要在F206上实现所有的10中断是不可能的,所以我们利用CPLD,通过F206的8个数据线D0-D7对10中断进行了扩充。逻辑图如图4所示。

当HS3282产生中断时,心06通过这8个数据线读取中断信号(/DRII一/DR42,分别对应4块HS3282的/DRI、/DR2)并传输至F206。进行相应的中断控制;同时这8个数据线还作为F206向HS3282发出控制信号/MRI一舳4(主复位信号)和ENTXl一ENTX4(允许发送信号)的传输线,将控制信号传输给HS3282,如图4(a),显然,D0一D7是双向传输的。所以在设计时,采用三态缓冲器74240和八D触发器74273来实现它们的双向传输,如图4(b)。

3.2 HS3282时钟模块

根据板卡要求,HS3282的发射时钟有两个可选频率480 k和1M。我们利用一个48M的外部晶振来驱动,使得它通过CPLD进行100分频和48分频分别得到这两个频率。其中100分频通过两个10分频逻辑实现,48分频先后通过8分频和6分频逻辑来实现。

3.3其它逻辑模块

除上述几个模块外,CPLD中还集成了板卡地址选择模块、HS3282读写信号的产生模块、提高板卡可靠性的复位模块等等。由于这些模块实现简单,在此就不再一一详述了。

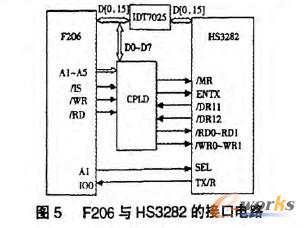

4 F206与HS3282的接口电路

F206与HS3282的接口电路如图5所示。

(1)/MR信号。主复位,低脉冲有效,通常只用于加电和系统重启。

(2)ENTX信号。发送使能标志,用于从先进先出存储器开始数据传输。

(3)TX/R信号。发送器输出标志,表明存储器空。

(4)/DR11和/DR12/信号。终端请求,通过数据线DO和D1将终端信号传输给F206。

(5)/RD信号。F206向HS3282发出的读取信号,用于读取HS3282缓存中的数据。

(6)/WR信号。F206向HS3282发出的写信号,用于向HS3282缓存中写数据。这只是17206与一片HS3282的接口电路,F206与其他3片HS3282的接口电路与之类似。

评论