一种智能ARI NC429总线接口板的硬件设计与实现

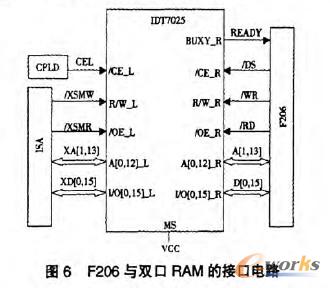

5 F206与双口RAM的接口电路

当接口板实现数据的发送功能时,数据首先从ISA总线读入,并存储在双口RAMIDTT025中,当适合发送数据时,F206发出读取信号,将存储在IDT7025中的数据通过DO~D15数据总线传输给HS3282,通过HS3282控制向429总线发送数据;同样,在接收数据时,HS3282接收的数据在砣06的控制下,通过数据总线DO,D15传输到IDT7025中,最后Pc机通过ISA总线接收数据,从而完成数据的收发功能。图6中,READY为高,表明对双口RAM的访问可以结束,否则将延续此次访问。

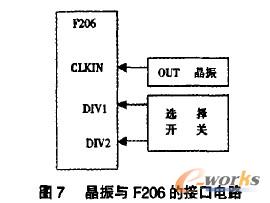

6 F206的时钟电路

DSP时钟可由外部提供,也可由板上的振荡器提供。但一般DSP系统中,经常使用外部时钟输入,因为使用外部时钟时,时钟的精度高、稳定性好、使用方便,从而可以保证DSP能够可靠、稳定的工作。而且,使用外时钟时,可以通过改变DIVI、DIV2引脚上的电平,设置时钟方式为×1、×2或×4。这样,只需用一个时钟。就可以提供DSP的多个工作时钟,增加了系统的灵活性。这里我们选用20M的晶振,并用选择开关来成比例的设置DSP的工作时钟。接口电路如图7所示。

7 仿真接口电路

DSP和CPLD都是通过仿真接口JTAG进行在线编程的。JTAG(Joint Test Action Group)是检测PCB和IC芯片的一个标准,通过这个标准,可对具有JTAG接口芯片的硬件电路进行边界扫描和故障检测。YrAG接口的设计比较简单,只要根据芯片所提供的接口类型按照相应的接口标准即可。

8 结束语

通过整个设计方案可以看出.用DSP+CPLD模式实现429总线和ISA总线之间的数据通讯,省去了EPROM、RAM、地址数据锁存器等外围电路,使得原理图的设计简单、清晰。合理地使用CPLD。又增强了板卡的集成度和开发的便利性。通过开发和调试证明,该板卡能够满足高速ARINC 429数据传输的要求,并且执行速度快,体积小,集成度高。可靠性好。

评论