片内时钟的组合思路和设计技巧

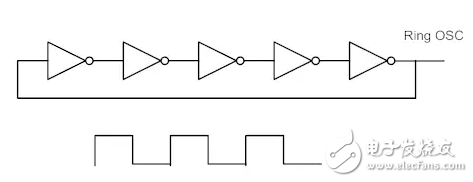

我们都知道,当奇数个反相器串联在一起,并且把最后一级的输出反馈给第一级的输入时,在逻辑上会产生震荡,这样的电路结构通常被称为Ring OSC。

本文引用地址://m.amcfsurvey.com/article/201710/365725.htm

那么在实际代码设计中,如何操作才能产生上述的电路结构呢?

我们先看第一种方法,尽管在ASIC设计中很常用,但是在FPGA设计中,一般是行不通的:

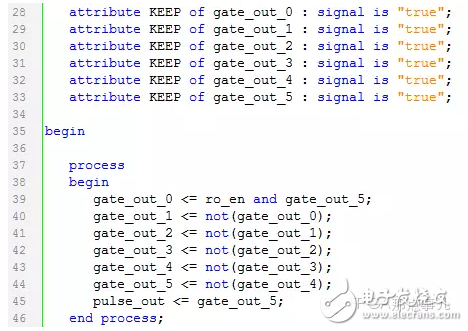

(1)第一种描述方法:

直接使用not语法对信号进行反向,并级联

这种方式,用ISE或者Vivado综合后,其实不会产生所需要的电路,因为从逻辑上讲,5个反相器进行级联其实和只是用1个反相器是等效的,所以综合工具仍然会把他们优化掉,即使对信号加了KEEP=true属性!

第二种处理方式才会产生真正想要的结果:

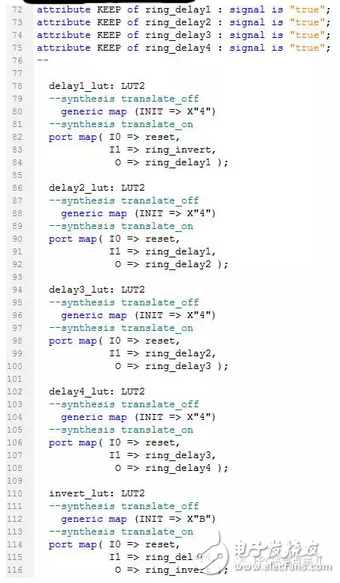

(2)第二种描述方法:

使用LUT做反相器进行级联

当然,通常的设计中,我们一般不会用到用这种方式产生的时钟。本文仅仅给大家提供一种思路和设计技巧,在我们设计其它特殊电路时,也许可以作为参考。

评论