AI架构创新和高端芯片发展

4 软件定义芯片架构

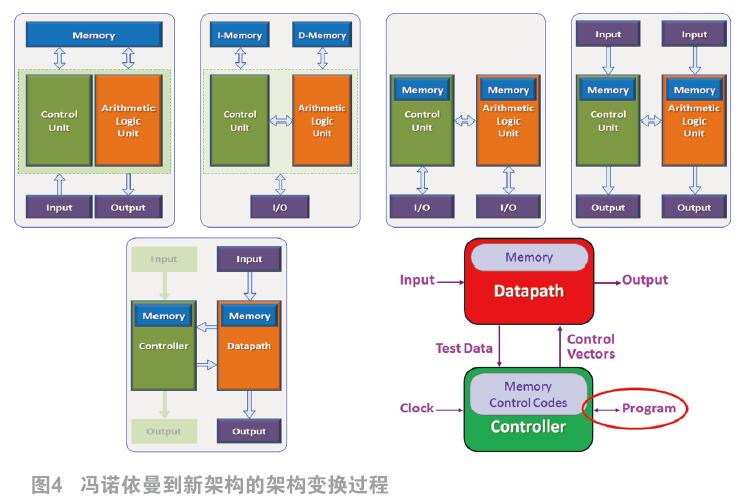

本文引用地址://m.amcfsurvey.com/article/201802/376161.htm如图3所示为基本冯诺依曼架构,包括控制单元、算数逻辑单元、存储器、输入和输出五个基本模块。首先将存储器分为两块,即I-Memory和D-Memory,分别对应指令和数据,这就是HUS结构。Input和Output合并,变成I/O;然后将存储器分别放入控制单元和算数逻辑单元,再将I/O分为两部分,一部分和控制单元相关,另一部分和数据逻辑单元相关;再将I/O分开,输入放在上边,输出放在下边;然后将这个结构逆时针旋转90度,得到的架构即为软件定义芯片架构(以下简称“新架构”)。冯诺依曼到新架构的架构变换过程如图4所示。

因此,该架构实际上是从经典的冯诺依曼架构变换得来。但是它和冯诺依曼体系结构又有所不同,即它不再使用指令集,而直接采用信息流,这也是两者间的本质区别。

另外,与传统架构比较,新架构还具有以下特点:

1)传统架构都是冯诺依曼等效架构,是刚性的;而功能化的硬件架构,是应用性的。

2)传统架构是应用去适应计算的架构,新架构是计算架构适应应用。即,传统架构是软件适用硬件,而新架构是硬件适用软件。

3)在传统架构中,一个任务一个软件;而在新架构中,一个任务会有多个等效软件。

4)在传统架构中,硬件和软件是不变的;在新架构中,硬件和软件是选择性动态改变的。

5)传统架构中,为了节省硬件资源,大量复用;新的架构中是使用冗余方式实现的。

5 计算模式的改善

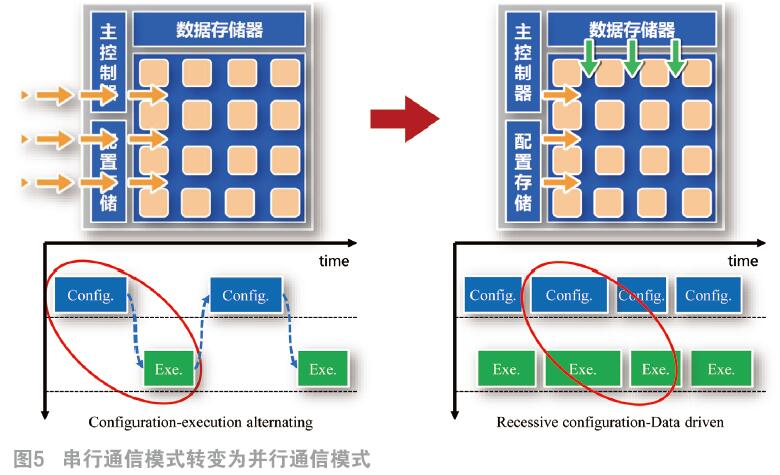

硬件配置时间和执行时间对于硬件架构来说是一个必须考虑的问题。当硬件配置时间多于执行时间时,显然是不经济,不合理的。而新架构在刚开始工作的时候,其中将近90%的时间都用来配置硬件,而只有10%的时间是用来进行计算和执行的。显然这样的架构需要进一步改善,主要通过以下两种方式进行改善:

1)首先将配置信息减少。通过采用诸如配置子图的方式、结构化组织等一系列方法,最终将配置信息减少将近80%。

2)数据不断写的过程也会耗费大量时间。很多数据写进去并不需要翻译,采用频次优先方法,用的最多的先写入,频次少的就不写入或少写入,这样可以将整个配置时间缩短12倍。

其计算模式变化如图5所示。传统架构是串行计算模式,而新架构则是交叉的并行计算模式。经过努力后,我们可以使一个阵列的计算时间占到整个运行时间的90%,而只有10%的时间用来实现配置。这样将多数时间用来计算的架构才是更合理的架构。

6 针对不规则阵列的架构改善

在上述例子中给出的是规则的运算阵列,而实际上的运算阵列是不规则的,有不同的密度,中间可能出现迭代和循环,分支长短可能不一。在规则的阵列上运行不规则的运算显然会出现效率的高低。

阵列是硬性放大的,我们无法改变硬件,因而只能改变软件,具体通过以下方法:

1)把软件并行化处理。特别是控制性的软件并行化处理,甚至在时空上也作相应的变换,让其在时空上也能并行化。

2)改变电源的供电情况。例如,在阵列中并非所有运算单元同时存在,这样就需要一部分打开,一部分关掉,由于完全关掉后重新启动需要很长时间,会降低性能,因而要使其部分处于浅度睡眠,有的进入深度睡眠,有的进入浅度睡眠,从而恢复的时候,节省启动时间。

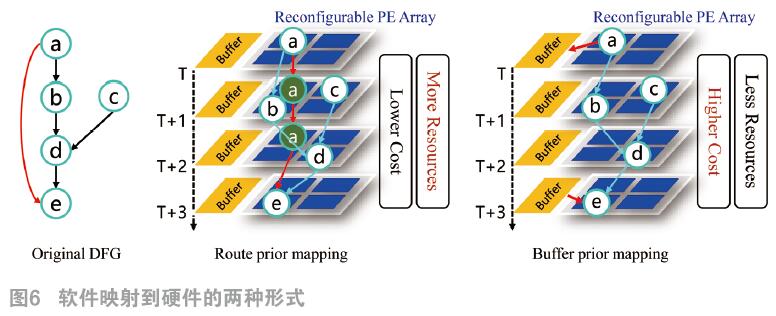

3)将软件映射到不同的硬件上。不同映射形式会带来不同的运算结果,这里给出两种不同的应对方法,如图6所示。a的数据走中间,可以通过route(计算资源)或者buffe(缓冲层)来传输,这两种传输方式哪种更适合新架构,还需要建立一整套模型,通过性能的模型实现各种仿生变换,最终确定最优的执行时间。如果建立面向性能的模型,可以使得性能提升20%;而如果建立面向功耗的模型,可以使功耗降低26%。但是,现在还无法建立两种模型的统一方案。

7 编程语言

全新的架构需要考虑全新的编程范式。传统硬件用C语言编程;而出现GPU后,随之而产生的是OpenCL编程语言;出现FPGA后,又有verilog、VHDL编程语言。而新架构软件的编程语言是基于传统编程语言,而基于原有的编程语言,语言不变、硬件不变的情况下,就需要去想新的编程范式。

FPGA很多时候是在编译时做分析,来进行决策。例如非功能运算是在运行过程中通过依赖关系来决定。这种方法有诸多不便。其中,依赖关系在编程序的时候就知道了,并非到运行的时候才会发现。新架构编程序的过程中就可以发现其依赖关系,在编译过程中就可以找到各个任务间的依赖关系,在运行的过程中保证其正确性就好。

新架构采用新的编程范式编写程序与采用OpenCL编写程序相比,速度提升了10倍;与英特尔的十核Xeon相比,性能仍有0.5~1.9倍的提升。

8 发展的机遇

把软件定于芯片的方式与传统的方式进行比较,新架构既具备ASIC的性能、功耗和特点,同时也保证了CPU的可读性,这样的结果还是很好的。当我们去做一个CPU、专用芯片或FPGA的时候,我们从定义开始出发,要完成一个电路设计,然后再去做其他的事情。如果你不懂电路设计,就无法运用FPGA进行设计。但是对于新架构而言,已经可以让软件设计工程师直接编程序,然后通过一个编译器直接映射到硬件上去。这里主要需要一个好的编译器,新架构的编译器汇集了大量的设计方法训练。

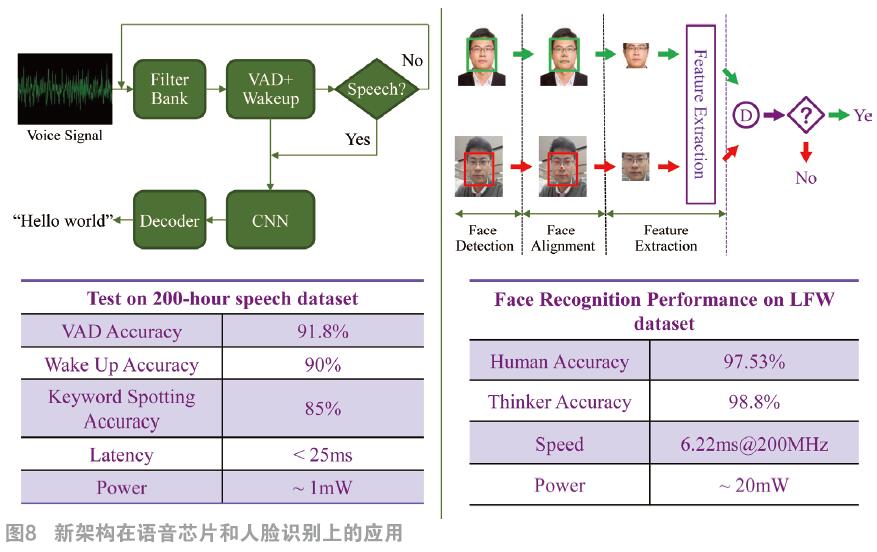

9 新架构的新应用

这样变化的结构可以应用到AI,AI还有很多新的变化,不同的应用或神经网络,我们能否通过变结构的方式,只要我们可以识别到一个具体的应用,识别出他用的是一个怎样的神经网络,就可以通过改变今天的功能来适应他,产生全新的发展呢?

如图8所示,采用新架构设计的语音识别芯片,精度已经可以达到91.8%,可以识别声纹,延时低达25 ms,功耗远远小于1 mW,应用到手机上几乎不耗电;右边是一个人脸识别,人脸识别结果最主要的是精度,可以达到99%,人类只能识别97%,工作在200 MHz,可以实现6 ms,运算功率,每瓦100万亿次的运算。

10 结论

芯片工艺技术进入10 nm,专用集成电路面临严峻的挑战,我们就该在架构上进行创新。其实在高端芯片上也是如此,如果跟着CPU的架构前进,我们永远是跟在别人后面的,能够在架构创新上超过别人才能引领时代。

硬件架构随着软件变化而变化的全新概念在保证芯片的功能满足要求的同时,又能保证其融合性,也是一项很好的创新。

本文来源于《电子产品世界》2018年第3期第25页,欢迎您写论文时引用,并注明出处。

评论