芯片封装技术这么多,常见的种类有哪些?

2、BQFP封装(quad flat packagewith bumper)

带缓冲垫的四侧引脚扁平封装。QFP封装之一,在封装本体的四个角设置突起(缓冲垫) 以 防止在运送过程 中引脚发生弯曲变形。美国半导体厂家主要在微处理器和 ASIC 等电路中采用 此封装。引脚中心距0.635mm, 引脚数从84 到196 左右(见 QFP)。

3、碰焊 PGA 封装 (butt joint pin grid array)

表面贴装型 PGA 的别称(见表面贴装型 PGA)。

4、C-(ceramic) 封装

表示陶瓷封装的记号。例如,CDIP 表示的是陶瓷 DIP。是在实际中经常使用的记号。

5、Cerdip 封装

用玻璃密封的陶瓷双列直插式封装,用于 ECL RAM,DSP(数字信号处理器)等电路。带有玻璃窗口的Cerdip

用于紫外线擦除型EPROM 以及内部带有 EPROM 的微机电路等。引脚中 心 距2.54mm,引脚数从8 到42。在日本,此封装表示为 DIP-G(G 即玻璃密封的意思)。

6、Cerquad 封装

表面贴装型封装之一,即用下密封的陶瓷 QFP,用于封装 DSP 等的逻辑LSI 电路。带有窗 口的 Cerquad用 于封装EPROM 电路。散热性比塑料 QFP 好,在自然空冷条件下可容许1. 5~ 2W 的功率。但封装成本比塑料

QFP 高3~5 倍。引脚中心距有1.27mm、0.8mm、0.65mm、 0.5mm、 0.4mm等多种规格。引脚数从32 到368。

带引脚的陶瓷芯片载体,表面贴装型封装之一,引脚从封装的四个侧面引出,呈丁字形。 带有窗口的用于 封装紫外线擦除型 EPROM 以及带有 EPROM 的微机电路等。此封装也称为 QFJ、QFJ-G(见 QFJ)。

7、CLCC 封装 (ceramic leadedchip carrier)

带引脚的陶瓷芯片载体,表面贴装型封装之一,引脚从封装的四个侧面引出,呈丁字形。带有窗口的用于封装紫外线擦除型 EPROM 以及带有 EPROM 的微机电路等。此封装也称为 QFJ、QFJ-G(见 QFJ)。

8、COB 封装 (chip on board)

板上芯片封装,是裸芯片贴装技术之一,半导体芯片交接贴装在印刷线路板上,芯片与基板的电气连接用引线缝合方法实现,芯片与基板的电气连接用引线缝合方法实现,并用树脂覆 盖以确保可*性。虽然 COB 是最简单的裸芯片贴装技术,但它的封装密度远不如 TAB 和倒片 焊技术。

9、DFP(dual flat package)

双侧引脚扁平封装。是SOP 的别称(见 SOP)。以前曾有此称法,现在已基本上不用。

10、DIC(dual in-line ceramic package)

陶瓷 DIP(含玻璃密封)的别称(见 DIP).

11、DIL(dual in-line)

DIP 的别称(见 DIP)。欧洲半导体厂家多用此名称。

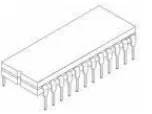

12、DIP(dual in-line package) 双列直插式封装。

插装型封装之一,引脚从封装两侧引出,封装材料有塑料和陶瓷两种。 DIP 是最普及的插装型封装,应用范围包括标准逻辑 IC,存贮器 LSI,微机电路等。

引脚中心距2.54mm,引脚数从6 到64。封装宽度通常为15.2mm。有的把宽度为7.52mm 和10.16mm 的封 装分别称为 skinny DIP 和 slim DIP(窄体型 DIP)。但多数情况下并不加区分,只简单地统称为 DIP。另外,用低熔点玻璃密封的陶瓷 DIP 也称为 cerdip(见cerdip)。

13、DSO(dual small out-lint)

双侧引脚小外形封装。SOP的别称(见 SOP)。部分半导体厂家采用此名称。

14、DICP(dual tape carrier package)

双侧引脚带载封装。TCP(带载封装)之一。引脚制作在绝缘带上并从封装两侧引出。由于利用的是 TAB(自 动带载焊接)技术,封装外形非常薄。常用于液晶显示驱动 LSI,但多数为定制品。另外,0.5mm 厚的存储器 LSI簿形封装正处于开发阶段。在日本,按照 EIAJ(日本电子机械工业)会标准规定,将 DICP 命名为DTP。

15、DIP(dual tape carrier package)

同上。日本电子机械工业会标准对 DTCP 的命名(见 DTCP)。

16、FP(flat package)

扁平封装。表面贴装型封装之一。QFP 或 SOP(见 QFP 和 SOP)的别称。部分半导体厂家采用此名称。

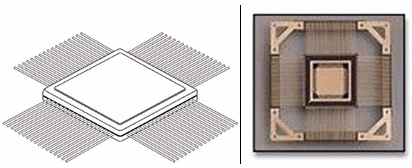

17、Flip-chip

倒焊芯片。裸芯片封装技术之一,在 LSI 芯片的电极区制作好金属凸点,然后把金属凸点与印刷基板上 的电极区进行压焊连接。封装的占有面积基本上与芯片尺寸相同。是所有封装技术中体积最小、最薄的一种。

但如果基板的热膨胀系数与LSI 芯片不同,就会在接合处产生反应,从而影响连接的可靠性。因此必须用树脂来加固 LSI 芯片,并使用热膨胀系数基本相同的基板材料。其中SiS 756北桥芯片采用最新的Flip-chip封装,全面支持AMD Athlon 64/FX中央处理器。支持PCI Express X16接口,提供显卡最高8GB/s双向传输带宽。支持最高HyperTransport Technology,最高2000MT/s MHz的传输带 宽。内建矽统科技独家AdvancedHyperStreaming Technology,MuTIOL 1G Technology。

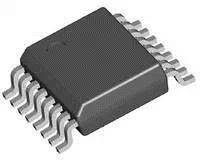

18、FQFP(fine pitch quad flat package)

小引脚中心距 QFP。通常指引脚中心距小于0.65mm 的 QFP(见 QFP)。部分导导体厂家采用此名称。塑料四边引出扁平封装 PQFP(Plastic Quad Flat Package)PQFP 的封装形式最为普遍。其芯片引脚之间距离很小,引脚很细,很多大规模或超大集成电路都采用这种封装形式,引脚数量一般都在100个以上。Intel 系列 CPU 中80286、80386和某些486主板芯片采用这种封装形式。 此种封装形式的芯片必须采用 SMT 技术(表面安装设备)将芯片与电路板焊接起来。采用 SMT 技术安装的芯片 不必在电路板上打孔,一般在电路板表面上有设计好的相应引脚的焊点。将芯片各脚对准相应的焊点,即可实现与主板的焊接。用这种方法焊上去的芯片,如果不用专用工具是很难拆卸下来的。SMT 技术也被广泛的使用在芯 片焊接领域,此后很多高级的封装技术都需要使用 SMT 焊接。

以下是一颗 AMD 的 QFP 封装的286处理器芯片。0.5mm焊区中心距,208根 I/O 引脚,外形尺寸28×28mm, 芯片尺寸10×10mm,则芯片面积/封装面积=10×10/28×28=1:7.8,由此可见 QFP 比 DIP 的封装尺寸大大减小了。

PQFP 封装的主板声卡芯片

19、CPAC(globetop pad array carrier)

美国 Motorola 公司对 BGA 的别称(见 BGA)。

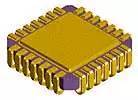

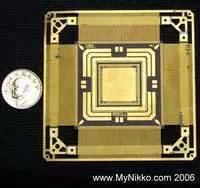

20、CQFP 用晶片陶瓷平版封b (CeramicQuad Flat-pack Package)

右@w晶片橐环N用晶片封b(CQFP),@是封b]被放入晶w以前的幼印_@N封b在用品以及航太工 I用晶片才有C到。晶片槽旁有厚厚的S金隔(有高起恚照片上不明@)用矸乐馆射及其他干_。 外有螺z孔可以⒕片牢牢固定在主C板上。而最有趣的就是四周的金_,@NO可以大大p少晶片封b的厚度K提供O佳的散帷

21、H-(with heat sink)

表示带散热器的标记。例如,HSOP 表示带散热器的 SOP。

22、Pin Grid Array(Surface Mount Type)

表面贴装型 PGA。通常 PGA 为插装型封装,引脚长约3.4mm。表面贴装型 PGA 在封装的 底面有陈列状的引脚,其长度从1.5mm 到2.0mm。贴装采用与印刷基板碰焊的方法,因而也称 为碰焊 PGA。因为引脚中心距只有1.27mm,比插装型 PGA 小一半,所以封装本体可制作得不 怎么大,而引脚数比插装型多(250~528),是大规模逻辑 LSI用的封装。封装的基材有多层陶瓷基板和玻璃环氧树脂印刷基数。以多层陶瓷基材制作封装已经实用化。

PGA 封装 威刚迷你 DDR333本内存

23、JLCC 封装(J-leaded chip carrier)

J 形引脚芯片载体。指带窗口 CLCC 和带窗口的陶瓷 QFJ 的别称(见 CLCC 和 QFJ)。部分半导体厂家 采用的名称。

24、LCC 封装(Leadless chip carrier)

无引脚芯片载体。指陶瓷基板的四个侧面只有电极接触而无引脚的表面贴装型封装。是高速和高频 IC 用 封装,也称为陶瓷 QFN 或QFN-C(见 QFN)。

25、LGA 封装(land grid array)

触点陈列封装。即在底面制作有阵列状态坦电极触点的封装。装配时插入插座即可。现已实用的有227 触 点(1.27mm 中心距)和447 触点(2.54mm 中心距)的陶瓷 LGA,应用于高速逻辑 LSI 电路。

LGA 与 QFP 相比,能够以比较小的封装容纳更多的输入输出引脚。另外,由于引线的阻抗小,对于高速 LSI 是很适用的。但由于插座制作复杂,成本高,现在基本上不怎么使用。预计今后对其需求会有所增加。

AMD 的2.66GHz 双核心的 Opteron F 的 Santa Rosa 平台 26、LOC 封装(lead onchip)

评论