极低功耗SoC设计方法学及EDA工具

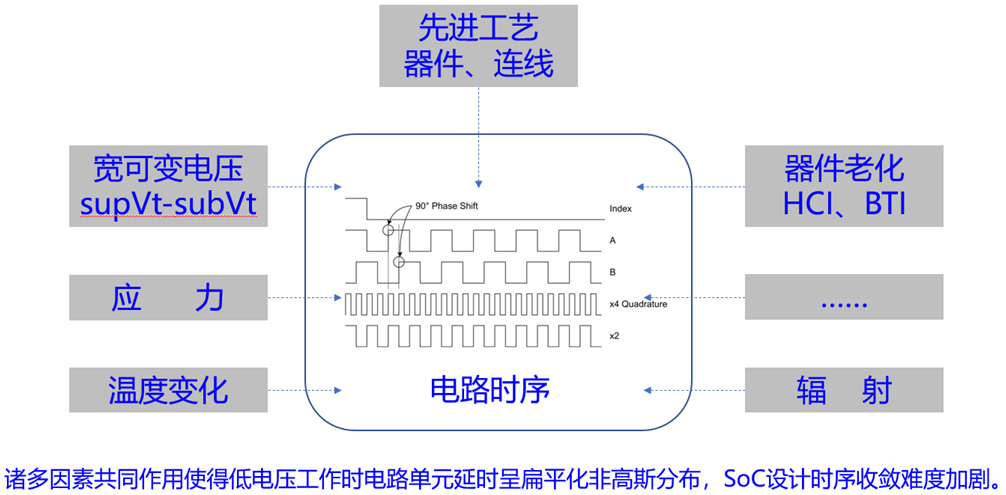

EDA中心在极低功耗SoC设计方法学及关键EDA技术领域开展了年的研发工作,研究设计了亚阈值温度传感器、32位亚阈值SAPTL超前进位加法器、16位亚阈值B-SAPTL加法器、16x16亚阈值ASYN-B-SAPTL异步乘法器、动态可重构亚阈值逻辑等多款极低功耗电路IP,技术指标均优于文献报道的同类功能电路,研发了单元电路版图微调软件、电路结构自动评测工具、电路器件参数优化工具、快速High-σ蒙特卡洛分析工具、器件建模工具、PVT敏感的单元电路特征化工具等。

本文引用地址://m.amcfsurvey.com/article/202204/433152.htm

极低功耗SoC设计方法学及关键EDA技术研究起因

评论