利用VectorBlox开发工具包在PolarFire FPGA实现人工智能

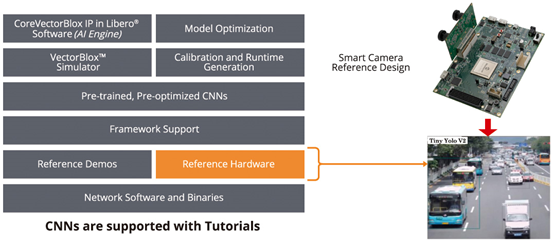

随着人工智能、机器学习技术和物联网的兴起,人工智能的应用开始逐渐转移到收集数据的边缘装置。为缩小体积、减少产热、提高计算性能,这些边缘应用需要节能型的解决方案。Microchip的智能嵌入式视觉解决方案,致力于让软件开发人员可以更方便地在PolarFire®现场可编程门阵列(FPGA)内执行人工智能的模型,进而满足边缘应用对节能型推理功能日益增长的需求。作为Microchip嵌入式解决方案组合的重要新成员,VectorBlox™加速器软件开发工具包(SDK)可帮助软件开发人员在不学习FPGA工具流程的前提下,利用MicrochipPolarFireFPGA创建灵活的低功耗神经网络应用。

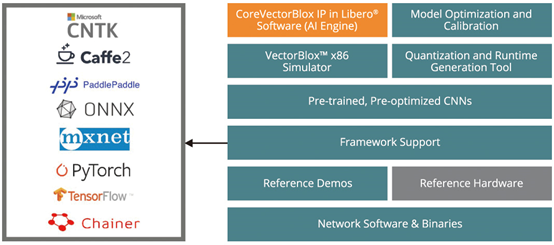

VectorBlox软件支持以下几个特性:

1.基于OpenVINO™工具包的前端工具;

2.支持最常见的框架,如TensorFlow、Caffe、MxNet、PyTorch和DarkNet;

3.无需预先了解FPGA即可快速评估;

4.基于软件覆盖的实现;更新CNN时无需重新编程FPGA。

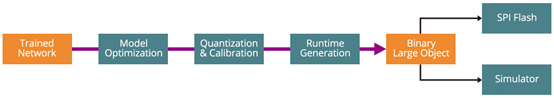

VectorBloxAccelerator SDK包含不同的工具,可将来自TensorFlow和ONNX等框架的神经网络描述编译成二进制大型对象(BLOB)。这些BLOB存储在闪存中,并在执行期间加载到 DDR 内存中。

主要几个工具如下:

1.模型优化:将经过训练的网络转换为通用的中间语言(IR),并通过删除训练期间使用的多个层以及优化网络以进行推理;

2.量化:将优化的网络从 FP32 转换为 INT8,并使网络能够使用更少的内存来表示,同时将精度损失降至最低;

3.校准:调整以INT8精度表示的模型的激活函数和权重;

4.运行时生成:创建写入嵌入式非易失性存储(例如 SPI 闪存)的BLOB。

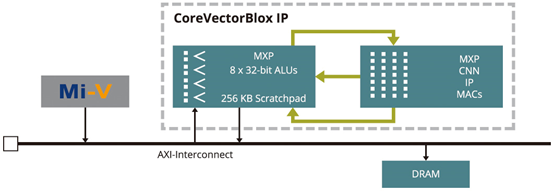

CoreVectorBlox IP是包含在SDK里面的硬件加速器,CoreVectorBlox IP由矩阵处理器(MXP)和MXP CNN IP组成。当需要共享神经网络工作负载时,它可以实例化为单核加速器或多核加速器。MXP由八个32位算术/逻辑单元(ALU)组成,负责按元素张量运算,如加、减、异或、移位、乘法、内积等。MXP CNN IP由乘法和累加的二维数组组成,IP使用FPGA内部的数学块来实现功能。顾名思义,MXP CNN IP负责执行CNN的卷积层。多个网络可以在运行时迭加并动态切换。

开发设计流程可以简单的分成三个步骤:

步骤1:准备训练好的模型

使用SDK中提供的Python脚本将经过训练的模型转换为优化的INT8表示形式,称为BLOB。通过VectorBlox Accelerator Simulator运行BLOB,以验证网络的准确性并确保网络的成功转换。

步骤2:准备硬件

PolarFireFPGA视频套件配置为作为支持AI的智能相机运行。SDK包括一个预编译的套件刻录档。使用套件中包含的FlashPro编程器将刻录档写入PolarFire FPGA并将第1步生成的BLOB写入套件的SPI闪存。

步骤3:编写您的嵌入式代码

在基于C/C++的SoftConsole IDE中使用提供的嵌入式代码并生成和编程hex文件。将视频套件连接到HDMI显示器并将其打开。修改嵌入式代码以加载和运行多个CNN BLOB、实时动态切换CNN或按顺序加载CNN以进行同时推理。

部署选项:

PolarFire FPGA视频套件(MPF300-VIDEO-KIT-NS)支持VectorBlox SDK。

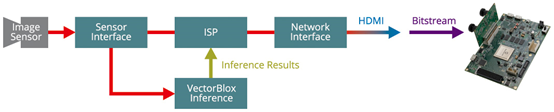

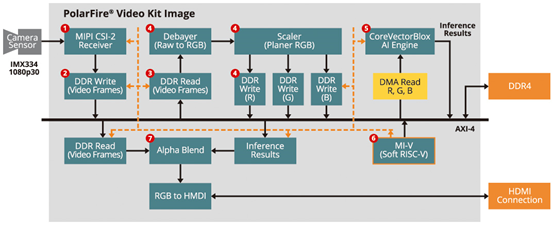

VectorBlox智能相机参考设计流程:

1.通过MIPI CSI-2接收影像;

2.影像存储在DDR4内存中;

3.推理之前,影像从DDR4读回;

4.影像从RAW转换为RGB并写回DDR4;

5.CoreVectorBlox引擎对R、G、B数组运行推理并将结果写回内存;

6.Mi-V(软RISC-V®)生态系统对概率进行排序并创建带有边界框的覆盖框架,并将结果放入 DDR4;

7.读取原始影像并与迭加帧进行 alpha 混合,然后发送到 HDMI 显示器。

本文作者为:Microchip高级应用工程师 张长轩

评论