基于FPGA的NAND Flash的分区续存的功能设计实现

0 引言

随着现代技术的发展,越来越多的系统采用NAND Flash芯片实时记录数据, 越来越大的NAND Flash容量让系统可以存储更大量的数据和更长的时间。但是,随着系统的变得复杂,对数据的存储也提出了更高的要求。传统的NAND Flash控制器每次存储都是从Flash 的零地址开始,本次存储任务结束后,当系统再次开启存储后,再次从零地址开始存储。新的数据会写覆盖之前的数据,无法实现数据的续存,使得NAND Flash使用起来十分不便;而且数据反复地从零地址开始存储,造成NAND Flash存储器的使用上的不均衡,影响其寿命[1]。

本文提出了一种基于FPGA的NAND Flash分区续存功能的控制器实现方法:NAND Flash控制器根据控制对象的特点,将NAND Flash划分多个分区,利用其自身的某一空间记录最新的分区地址信息,控制器在初始化时通过读取最新的分区地址信息,自动跳过该分区,在下一分区开始存储,同时更新最新的分区地址信息。通过这种方法,可以灵活地实现NAND Flash 控制器分区续存的功能,解决了数据不能续存的问题,同时也解决了NAND Flash 存储器的使用的不均衡的问题。

1 电路说明

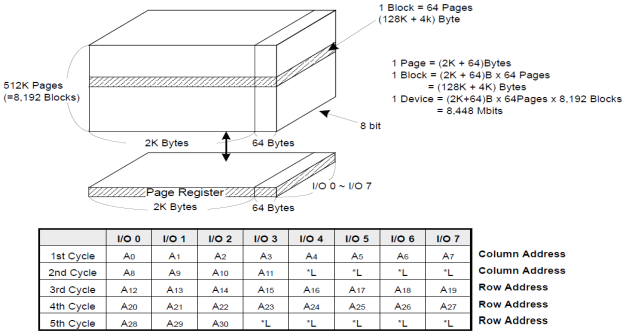

NAND Flash芯片使用型号是三星公司的K9K8G08U0A,单片容量为1 G x 8 Bit。该芯片总共有8 192 个块(Block),每个块中含有64 页(Page),每页共2112 个字节(前2 048 个主存储空间+64 个扩展空间)。芯片容量结构如图1 所示。

图1 NAND Flash内部存储空间结构图

FPGA使用型号为Xilinx 公司Virtex II 系列的XC2V1000,芯片内部有5 120 个Slice、40 个乘法器、720 kbit 的RAM 模块资源、320 个用户I/O 引脚。

2 NAND Flash控制器设计

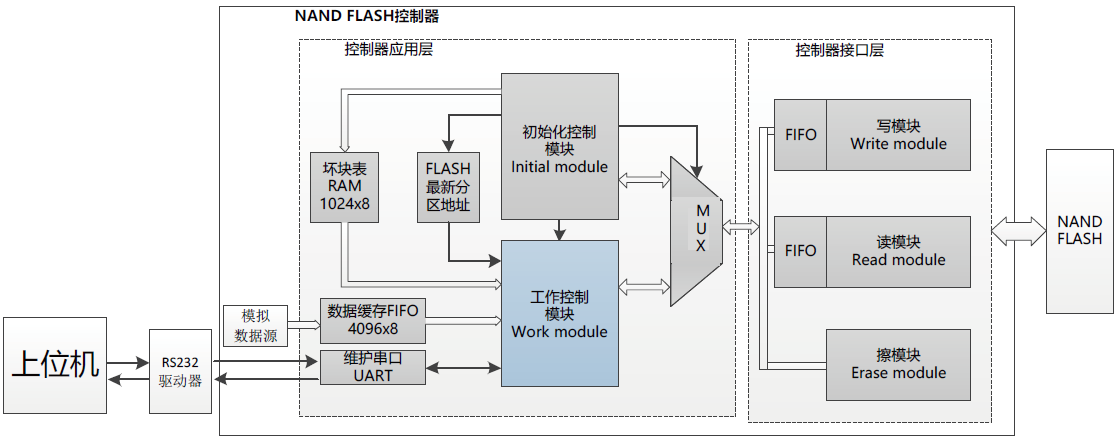

2.1 控制器概述

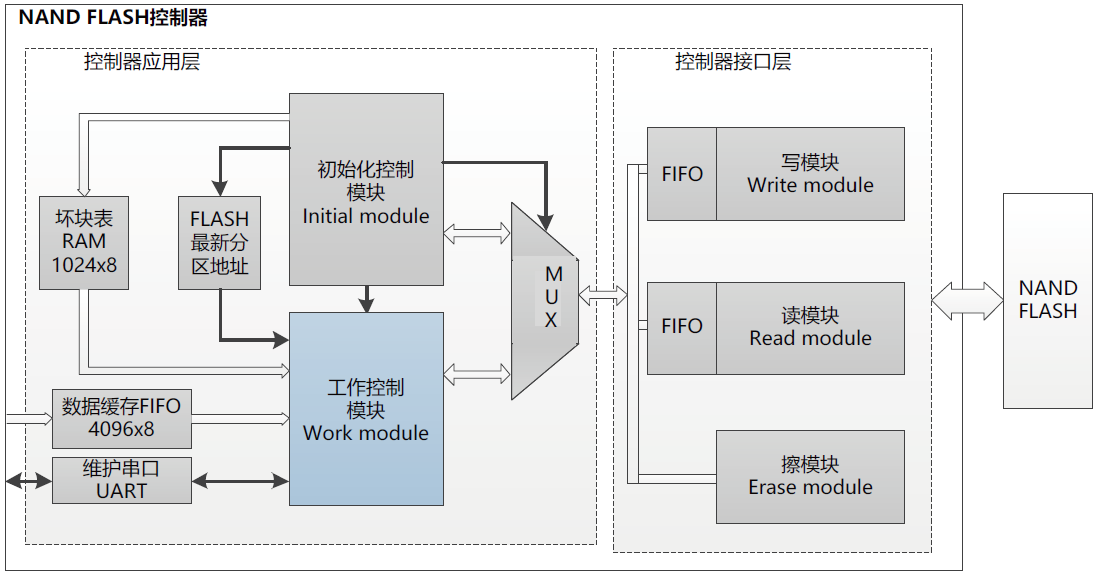

NAND Flash 控制器结构框图如图2 所示,一共分为应用层和接口层2 部分,接口层负责与NAND Flash的读、写,擦操作的接口;应用层负责调用接口层模块,同时完成NAND Flash 控制器的控制功能,分区续存功能设计在工作控制模块中[2]。

图2 控制器结构框图

2.1.1 分区设计

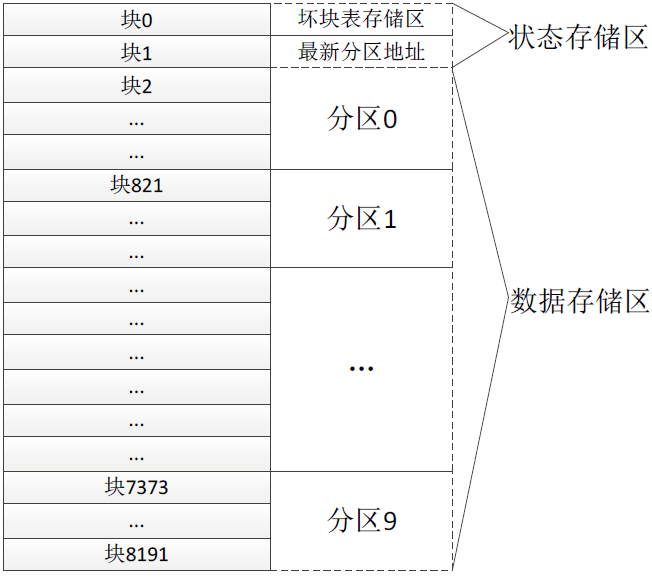

本型号NAND Flash 一共有8 192 个块,块地址从0~8 191。其中块0、块 1 用作状态存储区,其中块0 用于坏块表的存储,块1 用于存储本次数据记录用到的最新分区的地址信息;块2~ 块8 191 作用数据存储区,共计8 190 个块,在本设计中,将这8 190 个块分为10个分区,分别为分区0~9,每个分区有819 个块。分区设计结构如图3 所示[3]。

图3 NAND Flash分区结构

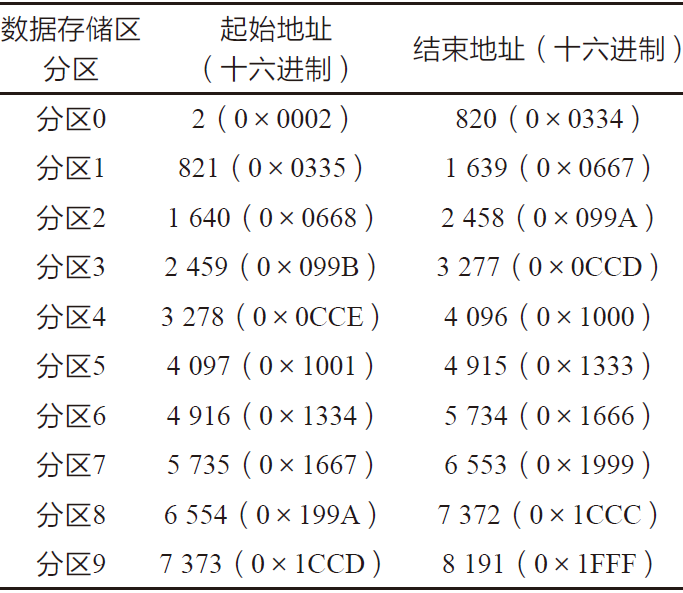

数据存储区的每个分区的起始地址和结束地址见表1。

表1 分区起始地址与结束地址

2.1.2 分区工作机理

NAND Flash 控制器上电后,需要先读取到上一次存储的NAND Flash 的分区地址信息,所以需要有一块专门的空间用于存储该地址[4-5]。在本设计中,利用NAND Flash 的块1 的第0 页专门的用于存储该地址信息,使用分区的起始地址作为分区的地址信息。

最新分区的地址信息需要动态更新。控制器获取起始地址信息后,根据分区大小,自动计算出下一分区的首地址作为本次存储操作的起始地址。控制器先将计算后的起始地址信息更新至块1 的第0 页处,然后从计算后的起始地址开始,进行数据存储操作。当数据存储操作超过本次分区的地址范围,则控制器在跨分区时,再次计算出下一分区的起始地址,并更新最新分区地址至块1 的第0 页处,从而实现了最新分区起始地址的实时更新[6]。

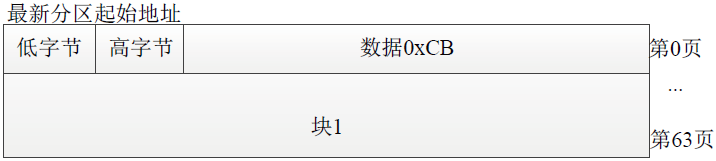

2.1.3 分区地址的存储

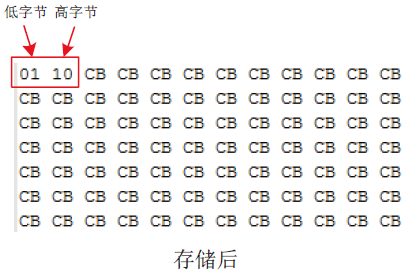

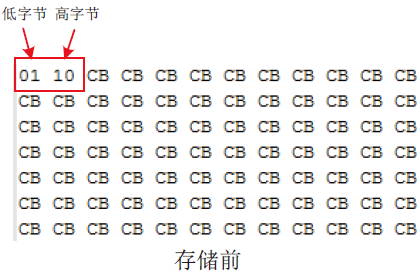

NAND Flash 存储器块1 中的第0 页为最新分区的首地址存储区,存储的数据格式如图4 所示。第0 页的第0、1 字节为最新分区首地址;第0 页的其他的数据皆为0xCB,该数据用于大量数据读取时的检索,能够方便地找到最新分区的首地址存储区。

图4 分区信息存储结构

由于块1 反复地被更新写入最新分区的起始地址,需要估算块1 的使用寿命:本次应用中,根据系统的要求,要存储的数据量为每间隔5 ms 存储256 个字节,可计算得到存储的数据量为51 kbit/s,则存满1 页需要40 ms,存满1 块需要2.56 s,存满1 个分区需要约38 min, 即大约每隔38 min 就要对块1 进行1 次写操作。根据NANDFlash 寿命按10 万次写操作计算[7],则NAND Flash 块1 在本系统中的使用时长约为6.3 万h,能够满足正常的使用需求。

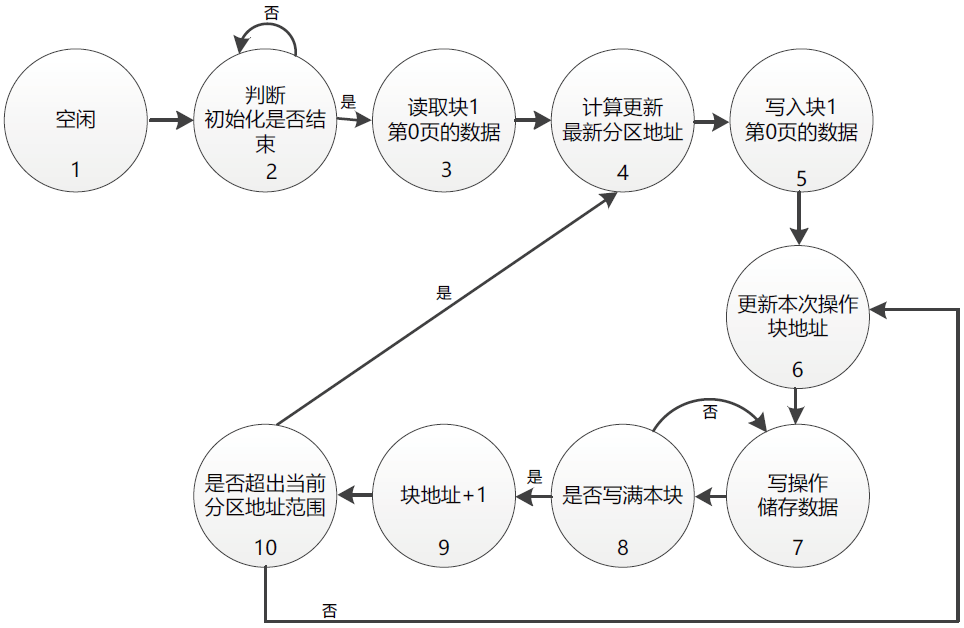

2.1.4 分区状态机的设计

根据分区机理,FPGA的工作控制模块设计了分区相关的状态机,状态机流程如图5 所示,状态跳转如下:上电后,状态机从状态1 跳转至状态2,判断初始化是否结束。等待初始化结束后,状态机跳转至状态3,读取块1的第0 页中的数据,得到上一次的分区信息;在状态4 中计算中更新本次要操作的最新的分区地址。状态机依次跳转至状态5、6,将更新后的最新分区地址写入块1 的第0 页,且更新本次操作的块地址。状态机跳转至状态6,进行正常的数据存储操作。状态7、8,9 为正常的连续写操作状态。状态10 时判断是否超出本分区,如果超出,则跳转至状态4 重新计算并更新分区地址,否则跳转至状态6 继续存储数据。

图5 状态机转换图

当电路下电,再次上电后,状态机会跳过上一次操作的分区,从下一分区开始存储数据,保证了数据存储的连续性,前一次的存储的数据不会被本次数据覆盖,本次数据前一次操作的分区的下一分区进行存储。

3 验证情况

验证的电路框图如图6 所示。在NAND Flash控制器中进行验证,分区功能嵌入在工作控制模块中,在FPGA 中设计1 个模拟数据源,模拟系统发送的数据,每隔5 ms 写入256 个字节数据;通过维护串口与上位机进行通信,可以通过上位机启动控制器工作和停止,读取块1 的数据等[8]。

图6 坏块表模块验证电路框图

验证内容分为两部分,首先为不跨分区的自动续存功能验证,其次为跨分区的自动续存功能验证。

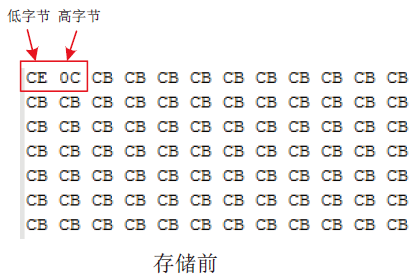

不跨分区验证时,验证的存储时长约为1 min。先通过维护串口与上位机发送读取命令,先读取块1 的数据,得到本次存储前的最新分区信息,然后发送存储命令,1 分钟后直接下电重启,再次读取块1 的数据,对比第2 次读到的最新分区信息,如图7 所示。存储前分区信息为0×0CCE,即分区4。存储后分区信息为0×1001,即分区5。说明本次存储的数据在分区5,成功跳过了分区4,分区4 为上一次存储的空间。

图7 不跨分区试验结果

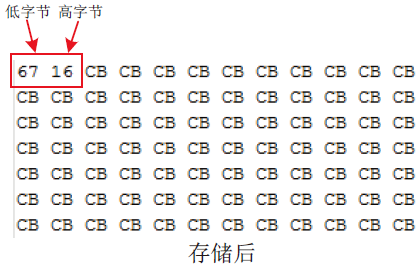

跨分区验证的存储时长约为45 min,大于38 min,以确保存储的数据能够超过1 个分区。先通过上位机发送读取命令,先读取块1 的数据,得到本次存储前的最新分区信息,然后发送存储命令,45 分钟后下电重启,再次读取块1 的数据,对比第2 次读到的最新分区信息,如图8 所示。存储前分区信息为0×1001,即分区5。存储后分区信息为0×1667,即分区7。说明本次存储的数据在分区6 和分区7,成功实现了跨过分区的存储和更新了最新分区地址信息。

图8 跨分区试验结果

综上,通过实验证明,本文设计的基于FPGA 的自动分区续存功能够正确地实现,方法简单便捷,满足系统对NAND Flash 存储器芯片的多次存储的控制需求。

4 结束语

本文提出了一种基于FPGA 的自动分区续存功能的方法,该方法简单方便的实现了存储器的分区管理,满足了数据分区续存的需求,并得到了试验证明。该方法的分区续存功能准确可靠,目前已经在实际产品中得到了应用和验证。

参考文献:

[1] 贾鑫,张少平.基于贪婪策略的NAND Flash存储器的磨损均衡算法研究[J].计算机科学,2017,44(11).

[2] 刘俊.基于FPGA的FLASH控制器设计[J].电子技术与软件工程,2016,23(11).

[3] 任勇峰,周涛.基于Flash的侵彻关键信号分区存储方法[J].探测与控制学报,2015,37(5).

[4] 李远哲,贺海文.嵌入式系统大容量NANDFlash存储器分区管理设计[J].计算机测量与控制,2019,2.

[5] 濮建福, 李世健.延长E E PROM使用寿命的均匀磨损算法[J].电子设计工程,2016,24(8).

[6] 邹姗蓉,李杰.基于FPGA的智能分区存储系统设计[J].电子器件,2016,39(6).

[7] 张卓,任家峪.一种基于NAND Flash基带数据模拟源的设计与实现[J].太赫兹科学与电子信息学报,2016,14(5).

[8] 张子明, 吴海建, 等. 基于F P G A的闪存XX29F系列读写装置的设计[J].测控技术,2016,35(7).

(本文来源于《电子产品世界》杂志2023年8月期)

评论