3D DRAM 设计能否实现?

如果说有一项技术的扩展效果不太好的话,那就是DRAM。造成这种情况的原因有很多:最重要的一个是DRAM单元的实际设计和制造关系。专门从事半导体电路设计的 Lam Research 发表了一篇论文,简述了未来DRAM产品的开发流程。

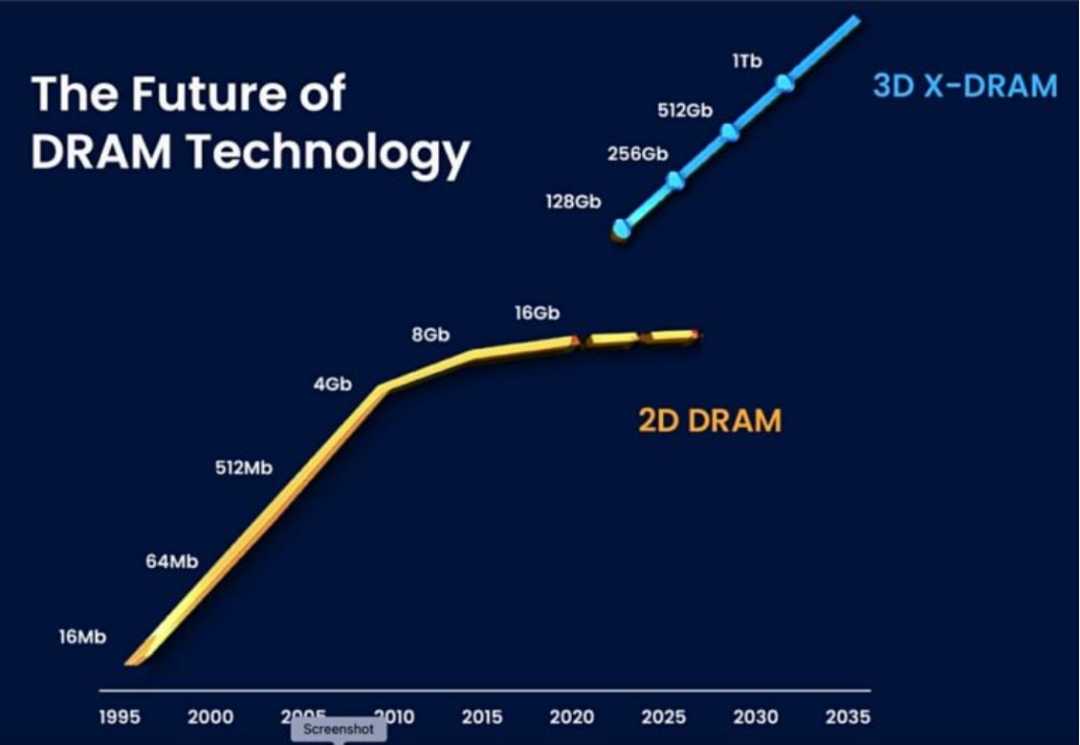

本文引用地址://m.amcfsurvey.com/article/202309/450573.htm综上所述,3D DRAM 的使用在未来或许是可能的。据该公司称,我们大约需要 5-8 年的时间才能设计出可制造的 3D DRAM 器件,2D DRAM 缩放结束与 3D DRAM 缩放开始之间可能存在三年的差距。

Lam Research 使用其专有的 SEMulator3D 软件分享了可能的 3D DRAM 设计。我们看到一些与缩放和层堆叠挑战、电容器和晶体管尺寸缩小、细胞间连接和过孔阵列(其他 3D 设计中使用的互连)相关的解决方案。最后,该公司列出了实现其拟议设计的工艺要求。

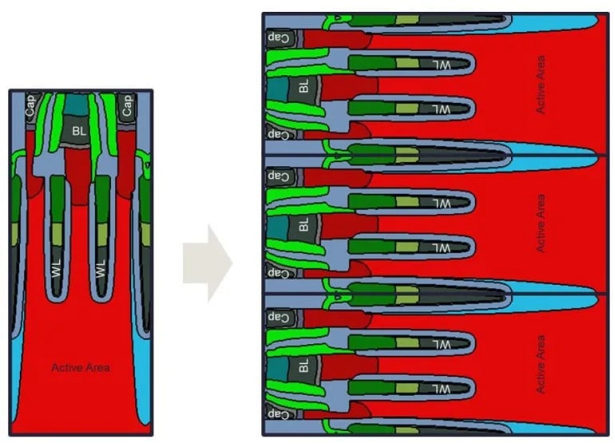

2D DRAM 架构的垂直视图(左),即当前 DRAM 架构中使用的相同设计。3D DRAM 示例,其中通过将芯片堆叠在一起来增加密度(右)。

由于 DRAM 单元的设计方式,不可能将 2D DRAM 组件横向放置并将它们堆叠在一起。这是因为 DRAM 单元具有高纵横比(它们的高度大于厚度)。将它们侧向倾斜需要超出我们当前的横向蚀刻(和填充)能力。

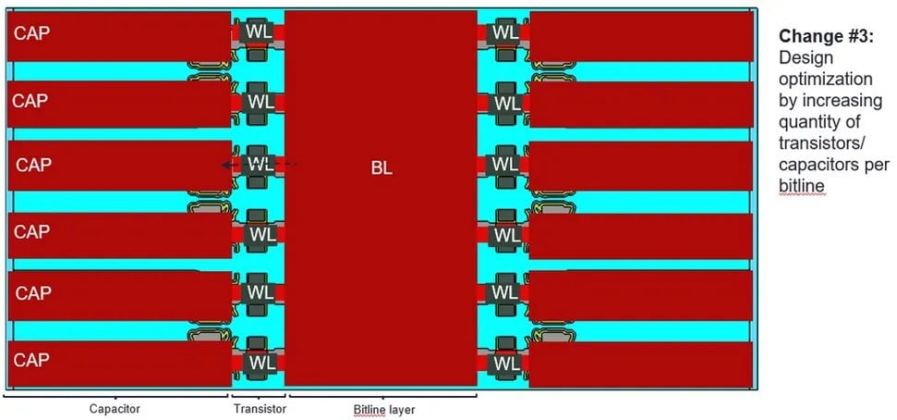

然而,当尝试解决设计约束时,可以根据需要进行一些更改和调整。这说起来简单,但实施起来却非常困难。当前的 DRAM 电路设计本质上需要三个组件:位线(注入电流的导电结构);晶体管,接收位线的电流输出,并作为栅极来控制电流是否流入电路(并充满电路);流经位线和晶体管的电流最终以位(0 或 1)的形式存储在电容器中。

Lam Research 使用了多种芯片设计「技巧」来实现工作架构。首先,他们将位线移至晶体管的另一侧。由于位线不再被电容器包围,这意味着更多的晶体管可以连接到位线本身,从而增加芯片密度。

Lam Research 的最终 DRAM 单元设计允许更多的晶体管通过相同的位线馈入,增加内存密度,同时「扁平化」设计,使其更适合 3D 缩放。

该设计电路的公司还应用了多种尖端晶体管制造技术,以最大限度地提高面积密度。其中包括英特尔正在研究下一代栅极技术的全环栅极 (GAA) 叉板设计。借助 Lam Research 提出的新 DRAM 架构,单元设计的各层可以相互重叠堆叠,就像 SSD 中的 NAND 一样。

链接

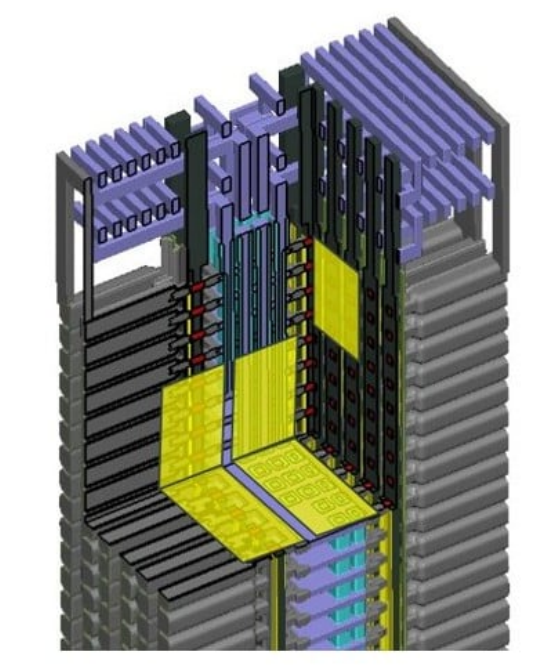

除了 3D DRAM 的新架构设计之外,互连技术也至关重要。Lam Research 推出了几种新方法,包括将栅极包裹在硅晶体管周围(全栅极)以及连接各层的水平 MIM(金属-绝缘体-金属)电容器阵列,以促进电流在中央位线堆栈上的移动。28 层 3D 设计的关键组成部分如下:

围绕栅极所有侧面的纳米层硅晶体管堆栈

两行晶体管之间的位线层堆叠

24 条垂直字线(DRAM 单元)

位线层和晶体管之间的多个桥连接;晶体管和电容器

一组卧式 MIM(金属-绝缘-金属)电容器

显示过孔序列的垂直结构特写。

可以像 NAND 一样开发

在领先公司的努力下,NAND 尺寸现已提升至 236 层。此外,三星计划在 2024 年开始生产 300 层 NAND 存储器。3D DRAM 设计还没有开始,它还处于起步阶段。在 Lam Research 讨论的设计中,估计第一代可能仅由 28 个堆叠层组成。然而,有人表示,如果这个问题得到解决,通过架构改进和附加层,DRAM 密度可以实现重大飞跃。正如我们在其他制造技术中看到的那样,可以使用通孔阵列(支撑 TSMC TSV 的互连技术)将各个层连接在一起。

至于不良部分,目前还没有生产设备能够可靠地生产所需的元件。该公司强调,如今 DRAM 设计还很不成熟,改进和重新设计工具和流程是普遍需求。因此,任何事情都还不算太晚,可以在不久的将来采取措施获得必要的工具。

3D X-DRAM 技术

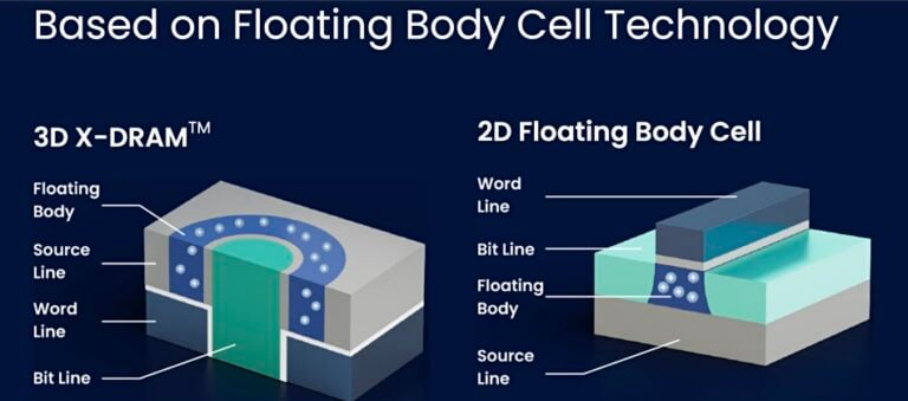

也有不同的公司关注这个问题。总部位于圣何塞的 NEO Semiconductor 今年详细介绍了其 3D X-DRAM 技术。这项 DRAM 专利技术的开发是为了「解决 DRAM 的容量瓶颈问题,并取代整个 2D DRAM 市场」。

根据该公司的路线图,在 DRAM 中实施类似 3D NAND 的 DRAM 单元阵列将使到 2030 年能够生产 1Tb 存储器。得益于 1 Tb(1 太比特)集成电路,单个 RAM 可以提供 2 TB 等大容量。如果使用 32 个独立芯片,4 TB 也可能实现。

大多数玩家仍然使用 8 GB 或 16 GB 内存。坦白说,3D X-DRAM 主要是用于服务器。当使用 32 个 32GB 芯片和当前 DDR4 内存技术时,每个 DIMM 可以为服务器提供高达 128GB 的容量。DDR5 DIMM 目前最高可达 64 GB。然而,更高容量的存储器即将出现。

NEO Semiconductor 受 3D NAND 技术(用于 SSD)的启发,开发了 3D X-DRAM 技术。USP 采用了号称「世界上第一个类 3D NAND DRAM 单元阵列」的解决方案来增加容量。

新的 DRAM 内存芯片将采用类似 3D NAND 的 DRAM 单元阵列。该公司声称,这一变化「简化了工艺步骤,提供了高速、高密度、低成本和高效率的解决方案。」

评论