micro SD卡

SD 卡很容易与 FPGA 连接。它们有不同的尺寸(标准、迷你和微型),但电气工作方式相同。我们重点讨论微型 SD 卡,因为它们小巧方便,如今也很流行。

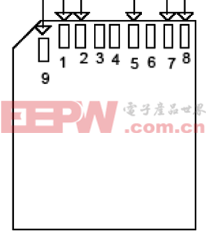

本文引用地址://m.amcfsurvey.com/article/202312/454089.htm微型 SD 卡有 8 个引脚。首先,电源连接在第 4 针和第 6 针上。

然后,根据您决定使用的操作模式,您需要将 3 到 6 个引脚连接到 FPGA 引脚。

SPI 模式

在 SPI 模式下,DI/DO 线路是单向的。这意味着

DI/DO 上无需上拉

命令(以及写扇区时的扇区数据)发送到 DI 引脚

从 DO 引脚接收响应(以及扇区读取时的扇区数据

SPI 模式通常用于微控制器系统。在 FPGA 中,我们可能更适合使用...

SD 模式

在 SD 模式下,CMD/DATx 线路是双向的。这意味着

CMD/DATx 上需要上拉(FPGA 通常可在内部提供上拉功能)

在 CMD 引脚上发送/接收命令/响应

从 DATx 引脚发送/接收扇区数据(用于扇区读取和写入

例如,在 SD 单位模式下,我们需要这些连接:

协议

SD 卡采用命令/响应方案工作。例如,命令 "17 "允许读取卡内存的一个扇区(512 字节)。所有通信都与主机(本例中为 FPGA)提供的时钟同步。启动时时钟频率应低于 400KHz,卡初始化后时钟频率可加快。

// we use the Xylo-E FX2 FIFO2 as data source for "commanding" an SD card // the SD card is used in one-bit SD mode // first we are going to drive the SD card at a much slower speed than the FPGA itself // let's create a "shift" signal that is asserted once every 64 clock periods reg [5:0] cnt=0; always @(posedge clk) cnt <= cnt+1; reg shift=0; always @(posedge clk) shift <= &cnt; // now we serialize every byte we get from the FIFO2 reg [2:0] cntbit=0;reg shifting=0; reg [7:0] data=0; always @(posedge clk) if(shift) shifting <= shifting ? ~(&cntbit & ~FIFO2_data_available) : FIFO2_data_available; always @(posedge clk) if(shift & shifting) cntbit <= cntbit+1; always @(posedge clk) if(shift) data <= (FIFO2_data_available & (~shifting | &cntbit)) ? FIFO_DATAIN : {data[6:0],1'b0};assign FIFO_RD = shift & (~shifting | &cntbit); // and send the serial data to the SD card assign SD_CLK = cnt[5]; assign SD_CMD = shifting ? data[7] : 1'bZ;所有命令和大多数响应的长度都是 48 位(6 字节)。扇区数据是 512 字节的倍数。例如,下面是一段可以向 SD 卡发送命令的简单代码。

评论